Research

本研究團隊致力於各式平行計算加速器(accelerator)之系統軟硬體與架構開發,隨著電晶體數量在晶片上的成長趨緩,以及通用型處理器(例如: CPU)在功耗上的瓶頸,面對一些擁有龐大計算量的應用(例如:深度學習),複雜的通用處理器架構設計無法滿足這些特殊領域應用的需求,因此如何設計特定領域加速器及其系統軟體,決定了下一個世代在各式創新應用上是否可以繼續成長的重要因素。我們實驗室的目標在於設計出高效能低功耗的特殊領域加速器(domain-specific accelerator)的系統軟體與硬體架構,提升各式特殊領域應用的計算速度,並降低晶片功耗的浪費。有別於以往的昂貴的ASIC non-recurring engineering (NRE)費用,現行的特殊領域加速器更著重在硬體的可重用性(reusability)和可程式化(programmability),為了達到這個目標,還需要透過在演算法上的調整,以及編譯器和runtime上的優化,才能使得該應用程式有效的利用計算加速器上的硬體資源,有效的提升其計算速度。TinyML Accelerators and Systems

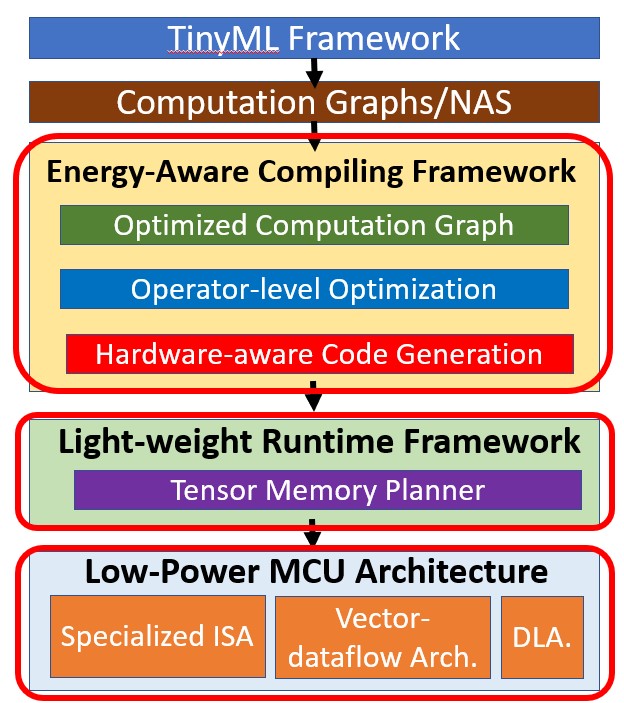

隨著IoT和TinyML的需求日漸增加,目前的Microcontroller (MCU)在計算能力和系統軟體支援上無法滿足新興應用的需求,因此我們目標在改良各式加速器架構以降低其功耗,並且設計編譯器和runtime system進一步的優化各式新興應用在加速器上的計算速度和記憶體空間管理。這個研究項目會參與嵌入式系統軟硬體的開發,相關技術和工具例如: TensorFlow Lite Micro, TVM, RISC-V ISA, Vector and dataflow processing

Chiplet-based Accelerators

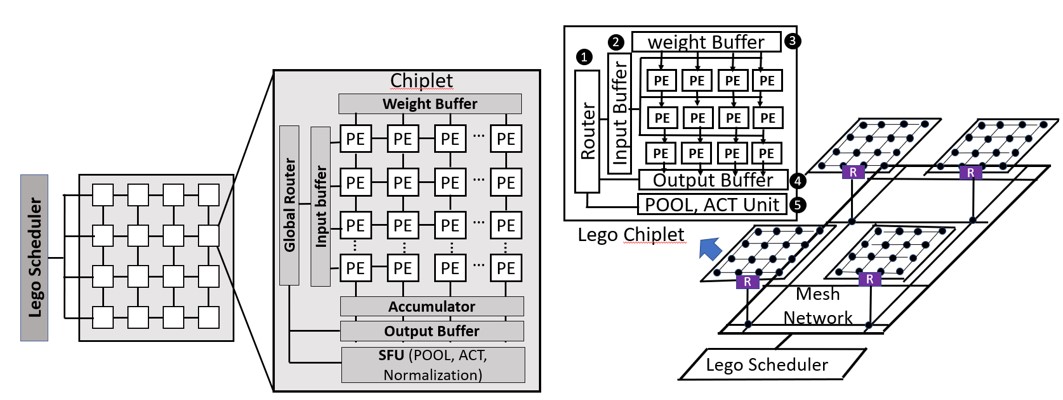

由於單一龐大晶片增加了晶片驗證的複雜度以及降低其容錯性,chiplet-based system將一個龐大的晶片切塊成多個晶片組,並透過了晶片內網路(NoC)以及interposer上的網路架構(Network-on-package(NoP))連結各個晶片組,以增加晶片上的平行度,chiplet-based架構已實現在現行許多產品上(例如: CPU,GPU,TPU),我們chiplet-based system研究重點著重在chiplet-based硬體資源上的配置以及NoC網路的設計。這個研究項目會接觸chiplet-based system和NoC模擬器開發並且透過RTL在FPGA上進行模擬和驗證

GPU

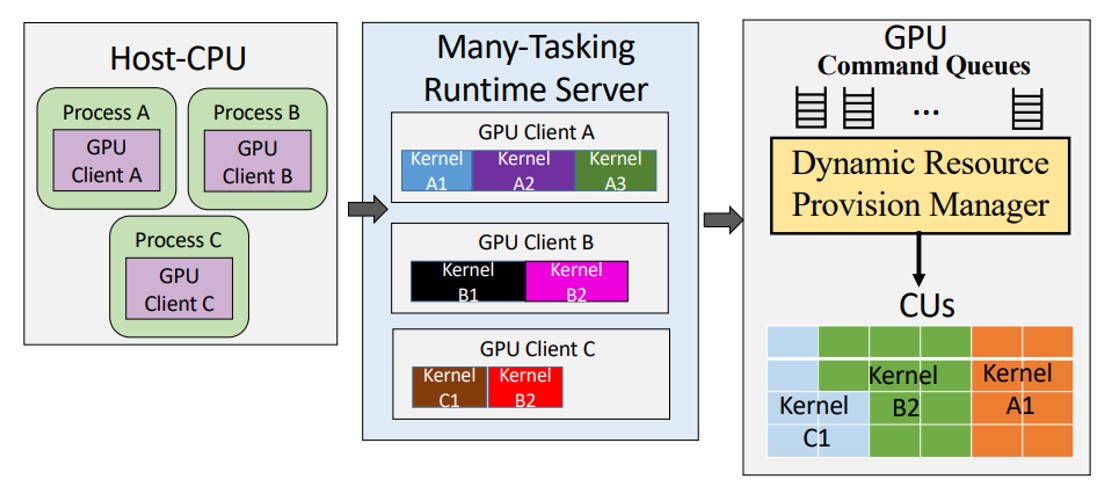

之前我們在GPU的研究方向著重在1)GPU硬體資源的虛擬化,2)降低GPU的冗餘計算,3)GPU並行運算的排程,但是隨著GPU在嵌入式裝置的角色越來越重要,我們研究方向著重改進GPU的架構以及改善3D圖形計算(例如:ray-tracing)的演算法,降低3D圖形計算的冗餘計算,功耗和速度。除此之外,我們也會持續開發在multi-GPU上的系統,提升multi-tenant DNNs應用或是graph processing的計算延遲和提升GPU硬體資源使用。這個項目會運用模擬器例如gpgpu-sim, gem5-apu或是改進既有深度學習架構(例如:TensorFlow, PyTorch, TensorRT)。

About

Location

- TEL: 886-03-5712121 #54744

- ADDR: EC120 Engineering Building III (工程三館)

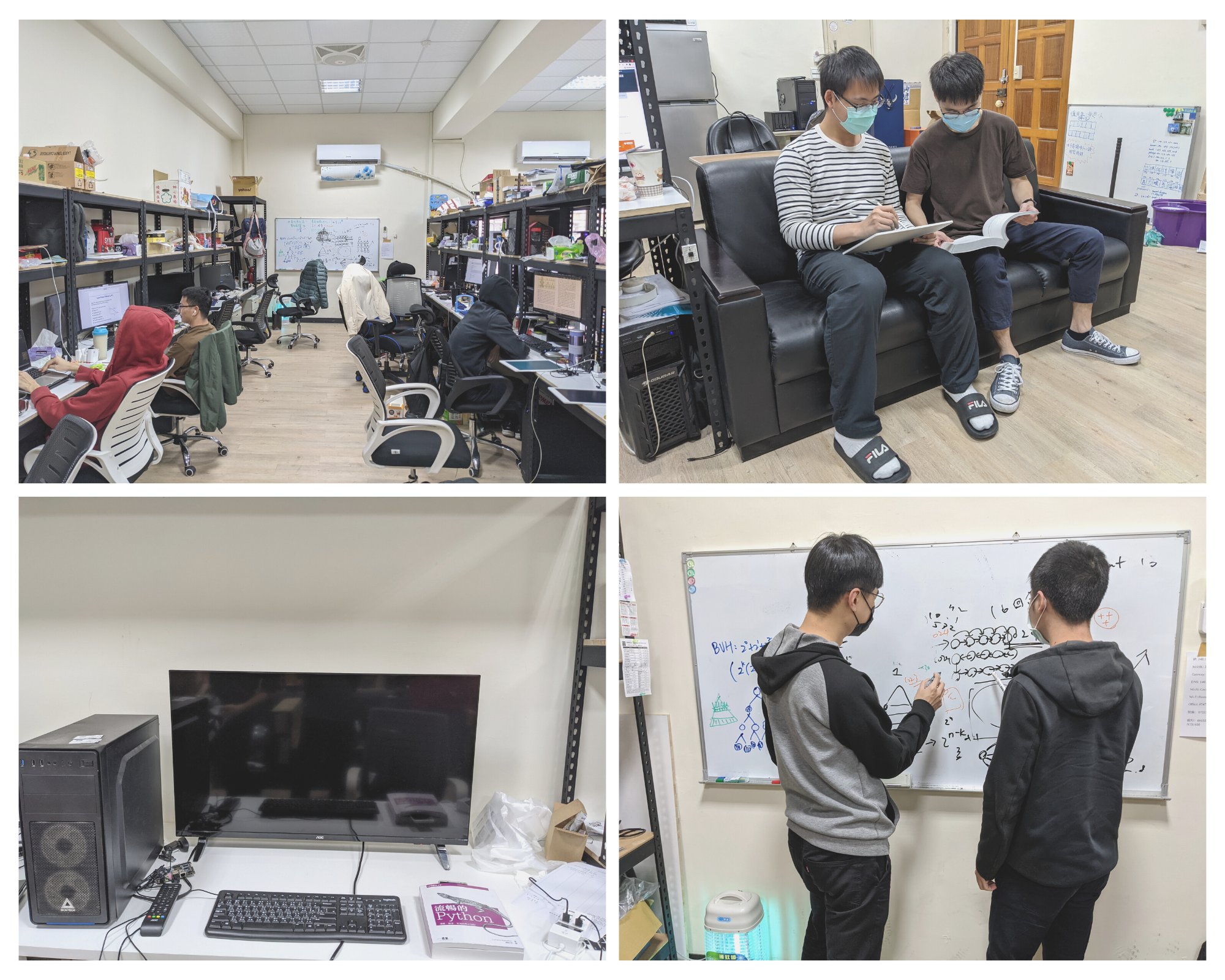

Environment

Students

Graduate students

- 2022

- Yu-Yuan Liu

- Bo-Ren Pao

- Zhi-Duan Jiang

- Chun-Yuan Teng

- Jen-Wei Huang

- Man-wen Su

- 2021

- Mu-Le Lee

- Kai-Chun Chang

- Ching-Jui Lee

- Guan-Wu Lin

- Hong-Yen Tai

- Cherie Hsieh

- 2020

- Meng-Hsien Lin (The first employment: MediaTek)

Master Thesis: Accelerating Graph Algorithms on GPGPU using Warp Balance - Chia-Wei Liu (The first employment: SiFive)

Master Thesis: Designing Energy-Efficient RISC-V Deep Learning Vector Accelerator - Keng-Ting Lin

Master Thesis: Evaluating AI Operators by Using Roofline Model - Bo-Cheng Chen (The first employment: TSMC)

Master Thesis: Evaluating the DNN Model Acceleration on Solid State Drive

Undergraduate students

- Heng-Chun Hung

- Yu-Fang Hu

- Yu-Ren Liu

- Yu-Yuan Liu