#### Lecture 3: ISA I

#### **CS10014 Computer Organization**

Tsung Tai Yeh Department of Computer Science National Yang Ming Chiao University

# Acknowledgements and Disclaimer

- Slides were developed in the reference with

- CS 61C at UC Berkeley

- https://inst.eecs.berkeley.edu/~cs61c/sp23/

- CS 252 at UC Berkeley

- https://people.eecs.berkeley.edu/~culler/courses/cs252-s05/

- E85 at HMC

- https://pages.hmc.edu/harris/class/e85/old/fall21/

# Outline

- Introduction

- Instruction Set Architecture (ISA)

- RISC-V Assembly Language

- Instructions

- Register Set

- Memory

- Programming constructs

#### Introduction

#### • Architecture:

- Programmer's view of computer

- Defined by instructions & operand locations

- Microarchitecture:

- How to implement an architecture in hardware (See single-cycle CPU lecture)

| Application<br>Software | >"hello<br>world!" |

|-------------------------|--------------------|

| Operating<br>Systems    |                    |

| Architecture            |                    |

| Micro-<br>architecture  |                    |

| Logic                   |                    |

| Digital<br>Circuits     |                    |

| Analog<br>Circuits      |                    |

| Devices                 | -                  |

| Physics                 |                    |

## Assembly Language

#### • Instructions:

- Commands in a computer's language

- Assembly language: human-readable format of instructions

- Machine language: computer-readable format (1's and 0's)

#### • RISC-V architecture:

- First open-source computer architecture

- RISC-V ISA manual

- https://riscv.org/specifications/isa-spec-pdf/

#### RISC-V 32-bit ISA

#### • RISC-V Base ISAs:

| Name   | Description                                                 |

|--------|-------------------------------------------------------------|

| RV32I  | 32-bit integer instruction set                              |

| RV32E  | 32-bit integer instruction set for embedded microprocessors |

| RV64I  | 64-bit integer instruction set                              |

| RV128I | 128-bit integer instruction set                             |

## RISC-V 32-bit ISA

#### • RISC-V Extensions:

| Suffix | Description                                                |  |  |  |  |  |

|--------|------------------------------------------------------------|--|--|--|--|--|

| Μ      | Standard extension for integer multiplication and division |  |  |  |  |  |

| А      | Standard extension for atomic instruction                  |  |  |  |  |  |

| F      | Standard extension for single-precision Floating Point     |  |  |  |  |  |

| D      | Standard extension for double-precision Floating Point     |  |  |  |  |  |

| С      | Standard extension for compressed instructions             |  |  |  |  |  |

| В      | Standard extension for bit manipulation                    |  |  |  |  |  |

| P/V    | Standard extension for packed-SIMD/vector instructions     |  |  |  |  |  |

## RISC-V 32-bit ISA

#### • RISC-V 32-bit ISAs:

- It supports 32-bit address spaces

- It contains thirty-three 32-bit registers

- It represents signed integer values in two's complement

- It contains integer computational/loads/stores instructions, and control-flow instructions

- It contains instructions to multiply and divide values held in the integer registers (M extension)

## Instructions: Addition

$\frac{\text{C Code}}{a = b + c;}$

RISC-V assembly code add a, b, c

#### • RISC-V assembly code

- add: mnemonic indicates operation to perform

- b, c: source operands (on which the operation is performed)

- a: destination operand (to which the result is written)

## Instructions: Subtraction

C CodeRISC-V assembly codea = b - c;sub a, b, c

#### • RISC-V assembly code

- sub: mnemonic

- b, c: source operands

- a: destination operand

## **Multiple Instructions**

| C Code         | RISC | -V a | ssen | nbly | co | de |   |   |   |   |

|----------------|------|------|------|------|----|----|---|---|---|---|

| a = b + c - d; | add  | t,   | b,   | С    | #  | t  | = | b | + | С |

|                | sub  | a,   | t,   | d    | #  | a  | = | t | _ | d |

More complex code is handled by multiple RISC-V instructions

# RISC vs CISC

#### • Make the common case fast

- RISC-V includes only simple, commonly used instructions

- Hardware to decode and execute instructions can be simple, small, and fast

- More complex instructions performed using multiple simple instructions

- RISC-V is a reduced instruction set computer (RISC) with a small number of simple instructions.

- Other architectures, such as Intel's x86, are complex instruction set computers (CISC)

- Operand location: physical location in computer

- Registers

- Memory

- Constants (also called immediates)

## **Operands: Registers**

- RISC-V has 32 32-bit registers

- Registers are faster than memory

- RISC-V called "32-bit architecture" because it operates on 32-bit data

- RISC-V also has 64-bit spec.

- RISC-V includes only a small number register

- Smaller is faster

#### **RISC-V** Register Set

| Name  | Register Number | Usage                              |

|-------|-----------------|------------------------------------|

| zero  | хO              | Constant value 0                   |

| ra    | x1              | Return address                     |

| sp    | x2              | Stack pointer                      |

| grp.  | x3              | Global pointer                     |

| tp    | x4              | Thread pointer                     |

| t0-2  | x5-7            | Temporaries                        |

| s0/fp | x8              | Saved register / Frame pointer     |

| s1    | x9              | Saved register                     |

| a0-1  | x10-11          | Function arguments / return values |

| a2-7  | x12-17          | Function arguments                 |

| s2-11 | x18-27          | Saved registers                    |

| t3-6  | x28-31          | Temporaries                        |

## **Operands: Registers**

#### • Registers:

- Can use either name (i.e., ra, zero) or x0, x1, etc.

- Using name is preferred

- Registers used for **specific purposes**:

- Zero always holds the **constant value 0**

- The remaining registers (x1-x31) are general purpose register and can be used interchangeably

- The **saved registers**, s0-s11, used to hold variables

- The **temporary registers**, t0-t6, used to hold intermediate values during a larger computation

## Instructions with Registers

• Revisit add instruction

*#* indicates a single-line comment

#### C Code

a = b + c;

a = b + 6;

**RISC-V** assembly code

| Name  | Register Number | Usage                          |  |  |  |  |

|-------|-----------------|--------------------------------|--|--|--|--|

| s0/fp | x8              | Saved register / Frame pointer |  |  |  |  |

| s1    | x9              | Saved register                 |  |  |  |  |

| s2-11 | x18-27          | Saved registers                |  |  |  |  |

## Operands: Memory

- Too much data to fit in only 32 registers

- Store more data in memory

- Memory is large, but slow

- Commonly used variables kept in registers

## Operands: Memory

• RV32I native datatypes and their respective sizes in bytes

| RV32I native data type name | Size in bytes |

|-----------------------------|---------------|

| Byte                        | 1             |

| Unsigned byte               | 1             |

| Halfword                    | 2             |

| Unsigned halfword           | 2             |

| Word                        | 4             |

| Unsigned word               | 4             |

Memory

- RISC-V is a Load/Store architecture

- Requires values to be loaded/stored explicitly from/to memory before operating on them

- Requires the data to be first retrieved from memory into a register by executing a load instruction

- First, we'll discuss word-addressable memory

- Then, we will discuss byte-addressable memory

**RISC-V** is **byte-addressable**

lw

add

SW

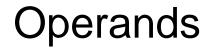

## Word-Addressable Memory

- Each 32-bit data word has a unique address

- 1 word = 4 bytes

# Reading Word-Addressable Memory

- Memory read called load

- Mnemonic: load word (lw)

- Format: <u>lw <rd>, <offset>(<base register>)</u> <u>lw t1, 5(s0)</u>

- Address calculation

- Add offset (5) to the base address (s0)

- Address = (s0 + 5)

- Destination register (rd)

- t1 holds the value at address (s0 + 5)

- Any register may be used as based address

# Reading Word-Addressable Memory

- Example:

- read a word of data at memory address 1 into s3

- Address = (0 + 1) = 1

- S3 = 0xF2F1AC07 after load

```

Assembly code

<u>lw</u> s3, 1(zero) # read memory word 1 into s3

```

| ١ | Nord Address |   | Data |   |   |   |   |   |   |        |

|---|--------------|---|------|---|---|---|---|---|---|--------|

|   | •            |   |      |   | • |   |   |   |   | •      |

|   | •            |   |      |   | • |   |   |   |   | •      |

|   | •            |   |      |   |   |   |   |   |   | •      |

|   | 0000003      | 4 | 0    | F | 3 | 0 | 7 | 8 | 8 | Word 3 |

|   | 0000002      | 0 | 1    | Е | Е | 2 | 8 | 4 | 2 | Word 2 |

|   | 00000001     | F | 2    | F | 1 | A | С | 0 | 7 | Word 1 |

|   | 00000000     | A | В    | С | D | E | F | 7 | 8 | Word 0 |

|   |              |   |      |   |   |   |   |   |   |        |

# Writing Word-Addressable Memory

- Memory write are called store

- Mnemonic: store word (sw)

- Format similar to load

#### sw <src1>, <offset>(<base register>)

# Writing Word-Addressable Memory

- Example:

- Write (store) the value in t4 into memory address 7

- t4 = 0x12345678

- Add the base address (zero) to the offset (0x7)

- Address: (0 + 0x7) = 7

- Offset can be written in decimal (default) or hexadecimal

| Assembly co      | ode           |          |       |        |       |

|------------------|---------------|----------|-------|--------|-------|

| <u>sw</u> t4, 01 | x7(zero)      | # writ   | e the | value  | in t4 |

|                  |               | # to m   | emory | word 7 |       |

| Word Address     | Data          |          |       |        |       |

|                  | 12345678      | , ₩o     | ord 7 |        |       |

| 0000003          | 40F3078       | 3 8 Word | 3     |        |       |

| 0000002          | 0 1 E E 2 8 4 | 12 Word  | 2     |        |       |

| 0000001          | F 2 F 1 A C 0 | 7 Word   | 1     |        |       |

| 00000000         | ABCDEF7       | 7 8 Word | 0     |        |       |

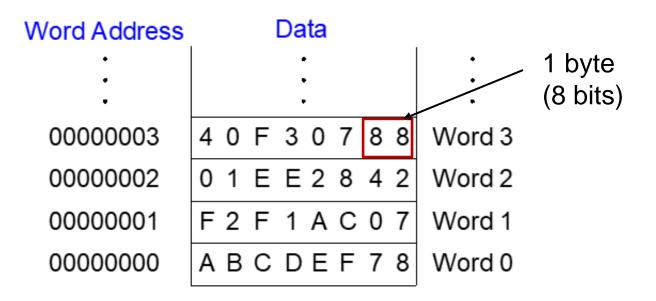

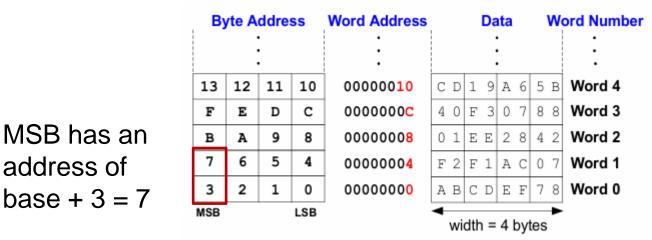

## Byte-Addressable Memory

- Byte addressable memory

- Each memory location stores a single byte and is associated with a unique address

## Byte-Addressable Memory

- Each data byte has unique address

- Load/store words or single bytes:

- load byte (lb) and store byte (sb)

- 32-bit word = 4 bytes, so word address increments by 4

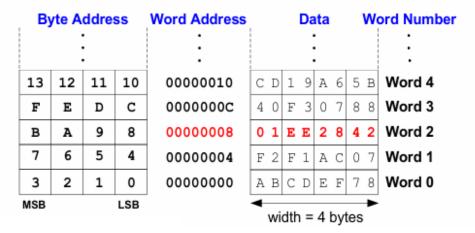

# Reading Byte-Addressable Memory

- The address of a memory word must be multiplied by 4

- Load a word of data at memory address 8 into s3

- s3 holds the value 0x1EE2842 after load

#### **RISC-V** assembly code

lw s3, 8(zero) # read word at address 8 into s3

# Writing Byte-Addressable Memory

- Example

- Store the value held in t7 into memory address 0x10 (16)

- If t7 holds the value 0xAABBCCDD, then after the sw completes, word 4 (at address 0x10) in memory will contain that value

**RISC-V** assembly code

| SW t7 | 7, 0 | x10                              | (ze  | ro) | # write      | t | 7      | i   | n  | tc | )   | ac  | ld | ress 16    |

|-------|------|----------------------------------|------|-----|--------------|---|--------|-----|----|----|-----|-----|----|------------|

|       | B    | yte A                            | ddre | SS  | Word Address |   |        |     | Da | ta |     |     | w  | ord Number |

|       | 13   | 12 11 10 0000010 A A B B C C D D |      |     |              | D | Word 4 |     |    |    |     |     |    |            |

|       | F    | E                                | D    | с   | 000000c      | 4 | 0      | F   | 3  | 0  | 7   | 8   | 8  | Word 3     |

|       | в    | A                                | 9    | 8   | 0000008      | 0 | 1      | Е   | Е  | 2  | 8   | 4   | 2  | Word 2     |

|       | 7    | 6                                | 5    | 4   | 0000004      | F | 2      | F   | 1  | A  | С   | 0   | 7  | Word 1     |

|       | 3    | 2                                | 1    | 0   | 0000000      | А | В      | С   | D  | Е  | F   | 7   | 8  | Word 0     |

|       | MSB  |                                  |      | LSB |              | 4 | wi     | dth | =  | 4  | bvt | tes | •  |            |

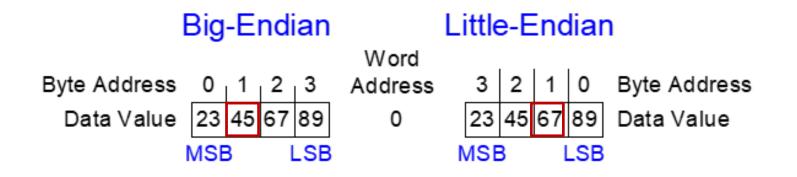

# Big-Endian & Little-Endian

- Little-endian

- Byte numbers start at the little (least significant) end

- Big-endian

- Byte numbers start at the big (most significant) end

- Word address is the same for big- or little-endian

| Bi              | g-E   | nd | ian             | Little-Endian |                 |      |   |   |     |  |

|-----------------|-------|----|-----------------|---------------|-----------------|------|---|---|-----|--|

| Byte<br>Address |       |    | Word<br>Address |               | Byte<br>Address |      |   |   |     |  |

|                 | · · · |    |                 | ÷             |                 |      |   |   |     |  |

| С               | D     | Е  | F               | С             |                 | FEDC |   |   | С   |  |

| 8               | 9     | А  | В               | 8             |                 | В    | А | 9 | 8   |  |

| 4               | 5     | 6  | 7               | 4             |                 | 7    | 6 | 5 | 4   |  |

| 0               | 1     | 2  | 3               | 0             |                 | 3    | 2 | 1 | 0   |  |

| MS              | B     |    | LSB             |               |                 | ISE  | 3 | l | _SB |  |

# Big-Endian & Little-Endian Example

- Suppose t0 initially contains 0x23456789

- After following code runs on **big-endian syst**em, what value is s0?

- In a little-endian system?

sw t0, 0(zero)

lb s0, 1(zero)

# Big-Endian & Little-Endian Example

- Big-endian

- s0 = 0x00000045

- Little-endian (RISC-V)

- s0 = 0x0000067

sw t0, 0(zero)

lb s0, 1(zero)

National Yang Ming Chiao Tung University Computer Architecture & System Lab

# Loading and Storing Bytes

- RISC-V has byte data transfers:

- Load byte: Ib

- Store byte: sb

- For example

- addi x11, x0, 0x3f5

sw x11, 0(x5)

lb x12, 1(x5)

- What is the value in x12?

- Note that 0x3f5 (HEX) = 0011 1111 0101(BIN)

3 f 5

0x3f5 = 1013(DEC)

| Answer | x12        |

|--------|------------|

| А      | 0x5        |

| В      | 0xf        |

| С      | 0x3        |

| D      | Oxffffffff |

## **Takeaway Questions**

- What is the value of RISC-V Register 1 (x1 = x0 + x0)?

- (A) 1

- (B) 0

- (C) 2

- What are advantages of the RISC instructions?

- (A) Reducing the complexity of the processor

- (B) Decreasing the number of executed instructions

- (C) Simplify the compiler design

National Yang Ming Chiao Tung University Computer Architecture & System Lab

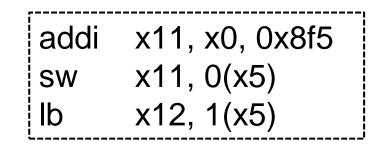

# **Takeaway Questions**

- What is the value in x12?

- (A) 0x8

- (B) 0xf8

- (C) 0xfffffff8

| addi | x11, x0, 0x8f5 |

|------|----------------|

| SW   | x11, 0(x5)     |

| lb   | x12, 1(x5)     |

# **Takeaway Questions**

- What is the value in x12?

- (A) 0x8

- (B) 0xf8

- (C) 0xfffffff8

Sign

| addi | x11, x0, 0x8f5 |

|------|----------------|

| SW   | x11, 0(x5)     |

| lb   | x12. 1(x5)     |

0x8f5 <=> 1000 1111 0101 (2' complement) <=> -779(DEC)

1000 1111 0101 (2'complement) -> -779 1000 1111 0100 (1' complement) 0111 0000 1011 (unsigned 779)

## **Takeaway Questions**

- What is the value in x12?

- (A) 0x8

- (B) 0xf8

- (C) 0xfffffff8

Sign

0x8f5 <=> 1000 1111 0101 (2' complement) <=> -779(DEC)

1111 1111 1111 1111 1000 1111 0101 (Signed extend 0x8f5 to 32-bits) => 0xfffff8f5

# **Takeaway Questions**

- What is the value in x12?

- (A) 0x8

- (B) 0xf8

- (C) 0xfffffff8

| addi | x11, x0, 0x8f5 |

|------|----------------|

| SW   | x11, 0(x5)     |

| lb   | x12. 1(x5)     |

- addi x11, x0, 0x8f5

- The immediate got sign extended, x11 is 0xfffff8f5 because x11 is signed 32-bit register

- sw x11, 0(x5)

- the value of x11 is copied to x5 = 0xffff8f5

# **Takeaway Questions**

- What is the value in x12?

- (A) 0x8

- (B) 0xf8

- (C) 0xfffffff8

- lb x12, 1(x5)

- Load byte sign extend to the register

- 0(x5) = 0xf5

- 1(x5) = 0xffffff8

## Programming

- High-level constructs

- Loops, conditional statements

- First, introduce:

- Logical operations

- Shifty instructions

- Generating constants

- Multiplication

## Logical Instructions

- and, or, xor

- and: useful for masking bits

- Masking all but the least significant byte of a value: 0xF234012F AND 0x000000FF = 0x0000002F

- or: useful for combining bit fields

- Combine 0xF2340000 with 0x000012BC 0xF2340000 OR 0x000012BC = 0xF23412BC

- **xor**: useful for inventing bits:

- A xor -1 = NOT A (remember that -1 = 0xFFFFFFFF)

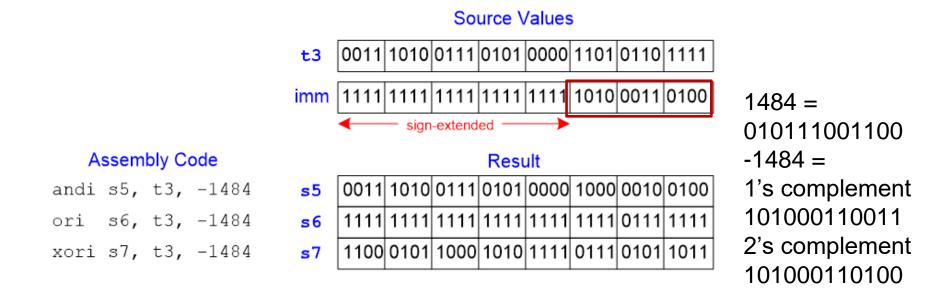

#### Logical Instructions Example

#### Source Registers

| s1 | 0100 0110 | 1010 0001 | 1111 0001 | 1011 0111 |

|----|-----------|-----------|-----------|-----------|

| s2 | 1111 1111 | 1111 1111 | 0000 0000 | 0000 0000 |

#### Assembly Code

| Recul  | ŧ  |

|--------|----|

| I LESU | L. |

| and | s3, | s1, | s2 | s3 |

|-----|-----|-----|----|----|

| or  | s4, | s1, | s2 | s4 |

| xor | s5, | s1, | s2 | s5 |

| 0100 0110 | 1010 0001 | 0000 0000 | 0000 0000 |

|-----------|-----------|-----------|-----------|

| 1111 1111 | 1111 1111 | 1111 0001 | 1011 0111 |

| 1011 1001 | 0101 1110 | 1111 0001 | 1011 0111 |

### Logical Instructions Example

-1484 = 0xA34 in 12-bit 2's complement representation.

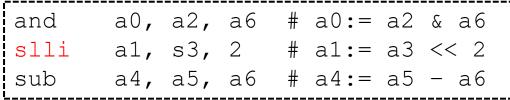

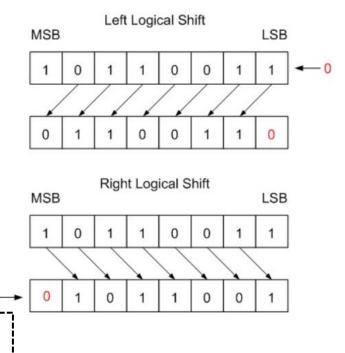

### Shift Instructions

#### Logical shift

- Correspond to (left-shift) multiplication by 2, (right-shift) integer division by 2.

- sll: shift left logical

- Example: sll t0, t1, t2 # t0 = t1 << t2</li>

- srl: shift right logical

- Example: srl t0, t1, t2 # t0 = t1 >> t2

### Shift Instructions

#### Arithmetic shift

- The sign is the leftmost bit, then arithmetic shift preserves the sign (this is called sign extension).

- sra: shift right arithmetic

- Example: sra t0, t1, t2 # t0 = t1 >>> t2

## Immediate Shift Instructions

- Shift amount is an immediate between 0 to 31

- slli: shift left logical immediate

- Example: slli t0, t1, 23 # t0 = t1 << 23

- srli: shift right logical immediate

- Example: srli t0, t1, 18 # t0 = t1 >> 18

- srai: shift right arithmetic immediate

- Example: srai t0, t1, 5 # t0 = t1 >>> 5

### **Generating Constants**

• 12-bit signed constants using addi:

C Code

RISC-V assembly code

// int is a 32-bit signed word

# s0 = a

int a = -372;

addi s0, 0, -372

Any immediate that needs more than 12 bits cannot use this method

# Generating 32-bit Constants

- Use load upper immediate (lui) and addi:

- **Iui**: puts an immediate in the upper 20 bits of destination register, 0's in lower 12 bits

| C Code              | <b>RISC-V</b> assembly code |

|---------------------|-----------------------------|

|                     | # s0 = a                    |

| int a = 0xFEDC8765; | lui s0, 0xFEDC8             |

|                     | <u>addi</u> s0, s0, 0x765   |

• Remember that addi sign-extends its 12-bit immediate

# Generating 32-bit Constants

- If bit 11 of 32-bit constant is 1, increment upper 20 bits ulletby 1 in lui

- if the MSB of the 12-bit constant (i.e. bit 11) is a 1, the constant is then sign extended.

#### C Code

# s0 = a

Note:  $-341 = 0 \times EAB$ int  $a = 0 \times FEDC 8 EAB;$

#

#### **RISC-V** assembly code

0xFFFFF = -1

Signed extension

s0, 0xFEDC9 # s0 = 0xFEDC9000 lui

addi s0, s0, -341 # s0 = 0xFEDC9000 + 0xFFFFFEAB

= 0xFEDC8EAB

$-341 = 0 \times EAB =$

1110 1010 1011

bit 11 of 32-bit

# **RISC-V:** Pseudo-instruction

- Load immediate 32-bit word is tedious

- Pseudo-instruction

- Assembler program translate "Load immediate" instruction "li" to two real RISC-V instructions: "lui" and "addi"

#### C Code

int a = 0xFEDC8EAB;

**Note:** -341 = 0xEAB

#### **RISC-V** pseudoinstructions

# s0 = a li s0, 0xFEDC**8E**AB

#### **RISC-V** real instructions

# s0 = a lui s0, 0xFEDC**9** addi s0, s0, 0xEAB

# **RISC-V:** Pseudo-instruction

- There is no instruction to load a register with a constant value

- To load s0 with the small constant 6, we use the instruction

- addi s0, zero, 6

- To load s0 with a large constant 0xFEDC8EAB

- Iui s0, 0xFEDC9

- addi s0, s0, 0xEAB

- To load a register with a constant of any size constant (up to 32 bits)

- li s0, 6

- li s0, 0xFEDC9

# RISC-V: Addressing Modes

- How do we address the operands?

- Register only

- Immediate

- Base addressing

- PC-relative

#### **Register Only**

- Operands found in registers

- Example: add s0, t2, t3

- Example: sub t6, s1, 0

#### Immediate

- 12-bit signed immediate used as an operand

- Example: addi s4, t5, -73

- Example: ori t3, t7, 0xFF

# RISC-V: Base + Offset Addressing

- Base Addressing

- Loads and Stores

- Base address + immediate

- Iw s4, 72(zero) # address = 0 + 72

- sw t2, -25(t1) #address = t1 25

- In C++, we call this a pointer it points to the place where the operand is stored

- An offset value must be a 12-bit 2's complement immediate constant

# **RISC-V: PC-relative Addressing**

#### PC-Relative Addressing: branch and jal Example:

| Address |     | Instruction    |

|---------|-----|----------------|

| 0x354   | L1: | addi s1, s1, 1 |

| 0x358   |     | sub t0, t1, s7 |

|         |     |                |

| 0xEB0   |     | bne s8, s9, L1 |

- The operand is derived from the Program Counter (PC) value by adding a 13-bit 2's complement offset

- The label is (0xEB0-0x354) = 0xB5C (2908) instructions before bne

- This type of addressing is ONLY used by the branch and jump instructions

## **Multiplication**

- 32 x 32 multiplication, 64-bit result

- mul s0, s1, s2

- s0 = lower 32 bits of result

- mulh s0, s1, s2

- s0 = upper 32 bits of result, treats operands as signed

- mulhu s0, s1, s2

- s0 = upper 32 bits of result, treats operand as unsigned

- mulhsu s0, s1, s2

- s0 = upper 32 bits of result, treats s1 as signed, s2 as unsigned

### Division

- 32 x 32 division, 32-bit quotient, remainder

- div s1, s2, s3 # s1 = s2/s3

- divu s1, s2, s3 # unsigned division

# **Control-flow Instructions**

- if statements

- if/else statements

- while loops

- for loops

## Branching

- Conditional branches

- branch if equal (beq)

- branch if not equal (bne)

- branch if less than (blt/bltu)

- branch if greater than or equal to (bge/bgeu)

- Unconditional branches

- jump (j)

- jump register (jr)

- jump and link (jal)

- jump and link register (jalr)

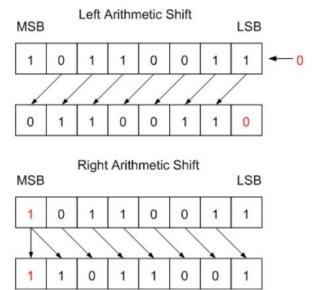

### Conditional Branching (beq)

# RISC-V assembly

| addi    | s0, zer | o <b>,</b> 4 | # s | 0 = 0 + 4 = 4  |

|---------|---------|--------------|-----|----------------|

| addi    | sl, zer | o, 1         | # s | 1 = 0 + 1 = 1  |

| slli    | s1, s1, | 2            | # s | 1 = 1 << 2 = 4 |

| beg     | s0, s1, | target       | # b | ranch is taken |

| addi    | sl, sl, | 1            | # n | ot executed    |

| sub     | sl, sl, | s0           | # n | ot executed    |

|         |         |              |     |                |

| target: |         |              | # l | abel           |

| add     | s1, s1, | s0           | # s | 1 = 4 + 4 = 8  |

• Label indicates instruction location. They can't be reserved words and must be followed by colon (:)

#### The Branch Not Taken (bne)

#### # RISC-V assembly

| addi | s0, | zero, 4    | # s0 = 0 + 4 = 4              |

|------|-----|------------|-------------------------------|

| addi | s1, | zero, 1    | # s1 = 0 + 1 = 1              |

| slli | s1, | s1, 2      | # s1 = 1 << 2 = 4             |

| bne  | s0, | sl, target | <pre># branch not taken</pre> |

| addi | s1, | sl, 1      | # s1 = 4 + 1 = 5              |

| sub  | s1, | s1, s0     | # s1 = 5 - 4 = 1              |

|      |     |            |                               |

|      |     |            |                               |

# Other Conditional Branches

Branch if less than (blt/bltu)

> blt s0, s1, target # branches if s0 < s1 (signed) bltu s0, s1, target

# same as <u>blt</u> but interprets # s0 and s1 as unsigned

Branch if great than (bge/bgeu)

> bge s0, s1, target # branches if s0 > s1 (signed) bgeu s0, s1, target # branches if s0 > s1 (unsigned)

## Unconditional Branching (j)

#### # RISC-V assembly

| j       | target |            | <pre># jump to target</pre> |

|---------|--------|------------|-----------------------------|

|         | srai   | sl, sl, 2  | <pre># not executed</pre>   |

|         | addi   | sl, sl, 1  | <pre># not executed</pre>   |

|         | sub    | s1, s1, s0 | <pre># not executed</pre>   |

|         |        |            |                             |

| target: |        |            |                             |

| add     |        | s1, s1, s0 | # s1 = 1 + 4 = 5            |

#### If Statement

C Code

RISC-V assembly code

# s0 = f, s1 = g, s2 = h

# s3 = i, s4 = j

bne s3, s4, L1

add s0, s1, s2

L1:

f = f - i;

sub s0, s0, s3

Assembly tests opposite case (i != j) of high-level code (i == j)

#### If/Else Statement

C Code if (<u>i</u> == j) f = g + h;else f = f - i;

RISC-V assembly code

# s0 = f, s1 = g, s2 = h

# s3 = i, s4 = j

bne s3, s4, L1

add s0, s1, s2

j done

L1: sub s0, s0, s3 done:

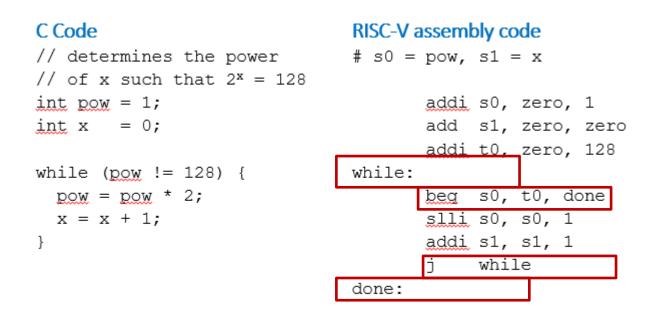

#### While loops

Assembly tests for the opposite case (pow == 128) of the C code (pow != 128).

#### For loops

for (initialization; condition; loop operation)

Statement

- Initialization: executes before the loop begins

- Condition: is tested at the beginning of each iteration

- Loop operation: Executes at the end of each iteration

- Statement: executes each time the condition is met

#### For loops

#### C Code

// add the numbers from 0 to 9

int sum = 0;

int i;

#### RISC-V assembly code

for:

|        | beq  | s0, | t0, | done |

|--------|------|-----|-----|------|

|        | add  | s1, | s1, | s0   |

|        | addi | s0, | s0, | 1    |

|        | j    | for |     |      |

| done : |      |     |     |      |

### Less Than Comparison

#### C Code

// add the powers of 2 from 1

// to 100

int sum = 0;

int i;

```

for (i=1; i < 101; i = i*2) {

sum = sum + i;

}</pre>

```

#### RISC-V assembly code

| #  | s0 | = | i,          | s1 | =  | รบ | ım    |    |     |

|----|----|---|-------------|----|----|----|-------|----|-----|

|    |    |   | ado         | li | s1 |    | zer   | Ο, | 0   |

|    |    |   | ado         | li | sC | ), | zer   | ο, | 1   |

|    |    |   | ado         | li | tC | ), | zero, |    | 101 |

| 10 | op | : |             |    |    |    |       |    |     |

|    |    |   | bge         | 2  | sC | ), | t0,   | do | one |

|    |    |   | ado         | ł  | s1 | ., | s1,   | s( | )   |

|    |    |   | <u>sl</u> ] | Li | sC | ), | s0,   | 1  |     |

|    |    |   | j           |    | 10 | op | )     |    |     |

| do | ne |   |             |    |    |    |       |    |     |

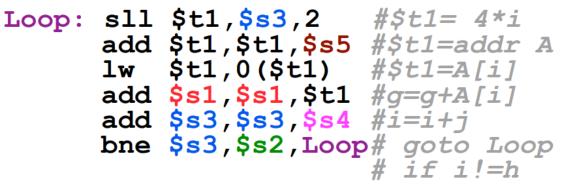

### Arrays

- Access large amounts of similar data

- Index: access each element

- Size: number of elements

### Arrays

- 5-element array

- Base address = 0x12348000 (address of first element, array[0])

- First step in access an array: load base address into a register

| 0x12340010 | array[4] |

|------------|----------|

|            |          |

| 0x1234800C | array[3] |

| 0x12348008 | array[2] |

| 0x12348004 | array[1] |

| 0x12348000 | array[0] |

|            |          |

|            |          |

|            | 1  <br>  |

#### **Accessing Arrays**

// C Code

int array[5]; array[0] = array[0] \* 2; array[1] = array[1] \* 2;

# # RISC-V assembly code # s0 = array base address lui s0, 0x12348

# 0x12348 in upper 20 bits of s0

| lw.<br>slli.<br>sw. | t1, 0(s0)<br>t1, t1, 1<br>t1, 0(s0) | <pre># t1 = array[0] # t1 = t1 * 2 # array[0] = t1</pre> |

|---------------------|-------------------------------------|----------------------------------------------------------|

| lm<br>slli          | t1, 4(s0)<br>t1, t1, 1              | <pre># t1 = array[1] # t1 = t1 * 2</pre>                 |

| sw                  | t1, 4(s0)                           | # array[1] = t1                                          |

#### Accessing Using For Loops

// C Code

int array[1000];

int i;

# RISC-V assembly code

# s0 = array base address, s1 = i

#### Accessing Using For Loops

#### # RISC-V assembly code

- # s0 = array base address, s1 = i

- # initialization code

| <u>lui</u> s0, 0x23B8F | # s0 = 0x23B8F000 |

|------------------------|-------------------|

| ori s0, s0, 0x400      | # s0 = 0x23B8F400 |

| addi s1, zero, O       | # <u>i</u> = 0    |

| addi t2, zero, 1000    | # t2 = 1000       |

| loop:                                                                              |

|------------------------------------------------------------------------------------|

| bge s1, t2, done # if not then done                                                |

| $\underline{slli}$ t0, s1, 2 # t0 = $\underline{i}$ * 4 (byte offset)              |

| add t0, t0, s0                                                                     |

| $\underline{1}_{W}$ t1, 0(t0) # t1 = array[ $\underline{i}_{J}$ ]                  |

| <u>slli</u> t1, t1, 3                                                              |

| $\underline{sw}$ t1, 0(t0) # array $[\underline{i}]$ = array $[\underline{i}]$ * 8 |

| addi s1, s1, 1 $\# i = i + 1$                                                      |

| j loop # repeat                                                                    |

#### ori:

**Description:** Performs bitwise OR on register rs1 and the signextended 12-bit immediate and place the result in rd Implementation: x[rd] = x[rs1] | sext(immediate)

# Unconditional Branching (j)

- j (jump)

- Perform an unconditional jump to a specified memory address.

- Used for implementing loops, conditional statements

```

C Code

RISC-V assembly code

// add the powers of 2 from 1

# s0 = i, s1 = sum

// to 100

addi s1, zero, 0

int sum = 0;

addi s0, zero, 1

int i;

addi t0, zero, 101

loop:

for (i=1; i < 101; i = i*2) {

s0, t0, done

bae

sum = sum + i;

s1, s1, s0

add

slli

s0, s0, 1

loop

done:

```

# Unconditional Branching (jal)

- jal (jump and link)

- performs an unconditional jump like "j," but it additionally stores the return address in a register

- commonly used for implementing procedure calls and function returns

allows a subroutine to jump to a target address and then return back to the original caller by using the stored return address.

#### Unconditional Branching (jr)

- jr (jump register)

- Used to perform an unconditional jump to an address specified in a register

- used for implementing function returns when the return address is stored in a register.

- # RISC-V assembly

| 0x00000200 | addi  | s0, | zero,  | 0x2 | 210 | )   |          |

|------------|-------|-----|--------|-----|-----|-----|----------|

| 0x00000204 | jr s0 | )   |        |     |     |     |          |

| 0x00000208 | addi  | s1, | zero,  | 1   | #   | not | executed |

| 0x0000020C | sra   | s1, | s1, 2  |     | #   | not | executed |

| 0x00000210 | lw    | s3, | 44(s1) |     |     |     |          |

# Unconditional Branching (jalr)

- jalr (jump and link register)

- combines the functionalities of "jal" and "jr."

- performs an unconditional jump to an address specified in a register and stores the return address in another register.

- used for function returns when the return address is stored in a register

#### Inequalities in RISC-V

- General programs need to test "<" and ">" as well

- Create a RISC-V Inequality instruction

- Set on Less Than

- Syntax: slt reg1, reg2, reg3

- Meaning: reg1 = (reg2 < reg3)

#### Inequalities in RISC-V

- For example

- if (g < h) goto Less; #g:\$s0, h:\$s1

- RISC-V code

- Branch if \$t0 != 0 -> (g < h)

- Register \$0/\$x0 always contains the value 0, so "bne" and "beq" often use it for comparison after an "slt" instruction

- A slt -> bne pair means if (... < ...) goto...

#### RISC-V Assembly Code Example

Search for the max value on an array

```

i /* Global array */

int numbers[10];

31

4 /• Returns the largest value from array numbers. •/

s int get_largest_number()

a (

int largest = numbers[0];

71

for (int i=1; i<10; i++) {

8

if (numbers[i] > largest)

<u>68</u>

largest = numbers[i]:

10

3

11

return largest;

12

13 }

```

#### **RISC-V** Assembly Code Example

```

1 .data

a # Allocate the numbers array (10 integers = 40 bytes)

a numbers: .skip 40

4.

s .text

ø get_largest_number:

la a5, numbers

# a5 := &numbers

2

lw a0. (a5)

# a0 (largest) := numbers[0]

81

li a1, 1

# a1 (i) := 1

<u>81</u>

li t4. 10

140

for:

11

bge a1, t4, end # if i >= 10, then exit the loop (end label)

12

slli t1, a1, 2 # t1 := i + 4

1.2

add t2, a5, t1 # t2 := &numbers + i+4

1.4

lw t3. (t2) # t3 := numbers[i]

1.5

blt t3, a0, skip # if numbers[i] < largest, then skip

146

a0. t3

# update largest

mv –

17.

skip:

1.8

addi a1, a1, 1 # i := i + 1

119

for

20

end:

21

ret.

# return

22

```

National Yang Ming Chiao Tung University Computer Architecture & System Lab

#### Takeaway Questions C Code: **RISCV (???)**: # $i \rightarrow s0$ , $j \rightarrow s1$ if(i<j) { a = b /\* then \*/# $a \rightarrow s2$ , $b \rightarrow s3$ } else { slt t0 s0 s1 a = -b / \* else \* /??? t0,???else What is ??? } then: In English: add s2, s3, x0 i end

- If TRUE, execute the <u>THEN</u> block

- If FALSE, execute the <u>ELSE</u> block

sub s2, x0, s3

else:

- What C code properly fills in the following blank?

- (A) j >= 2 && j < i

- (B) j < 2 || j < i

- (C) j < 2 && j >=i

do {i--; } while((z = \_\_\_\_));

```

Loop:

addi s0,s0,-1

slti t0,s1,2

bne t0,x0 Loop

slt t0,s1,s0

bne t0,x0 ,Loop

```

- What C code properly fills in the following blank?

- (A) j >= 2 && j < i

- (B) j < 2 || j < i

- (C) j < 2 && j >=i

do {i--; } while((z = \_\_\_\_));

| Loop: |                         | # i→s0, j→s1                    |

|-------|-------------------------|---------------------------------|

| addi  | s0,s0,-1                | # i = i - 1                     |

| slti  | t0 <b>,</b> s1,2        | # t0 = (j < 2)                  |

| bne   | t0,x0 Loop              | <pre># goto Loop if t0!=0</pre> |

| slt   | t0, <mark>s1</mark> ,s0 | # t1 = (j < i)                  |

| bne   | t0,x0 ,Loop             | <pre># goto Loop if t0!=0</pre> |

• Final compiled RISC-V assembly code:

• What is Original C codes of above assembly codes?

• Final compiled RISC-V assembly code:

• What is Original C codes of above assembly codes?

#### Conclusion

- Introduction

- Instruction Set Architecture (ISA)

- RISC-V Assembly Language

- Instructions

- Register Set

- Memory

- Programming constructs