# NAND Flash Controller

Lee Hao Zhi 2022/4/29

CONFIDENTIAL

# 新竹交大

- Duration: 2h/week

- Time: 10am-12pm

| Date | Торіс                                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4/29 | Lecture - Introduction to NAND Flash & Controller<br>Lecture - Introduction to FW concepts (basic)<br>Lab - FUSE environment set-up (before next lecture) |

| 5/6  | Lecture - Introduction to FW concepts (advanced)<br>Lab - Challenge                                                                                       |

| 6/B  | Students provide report and source code                                                                                                                   |

# **AGENDA**

NAND Flash Market NAND Flash Device FW Concepts (Basic) Summary

# NAND Flash Market

4

I II

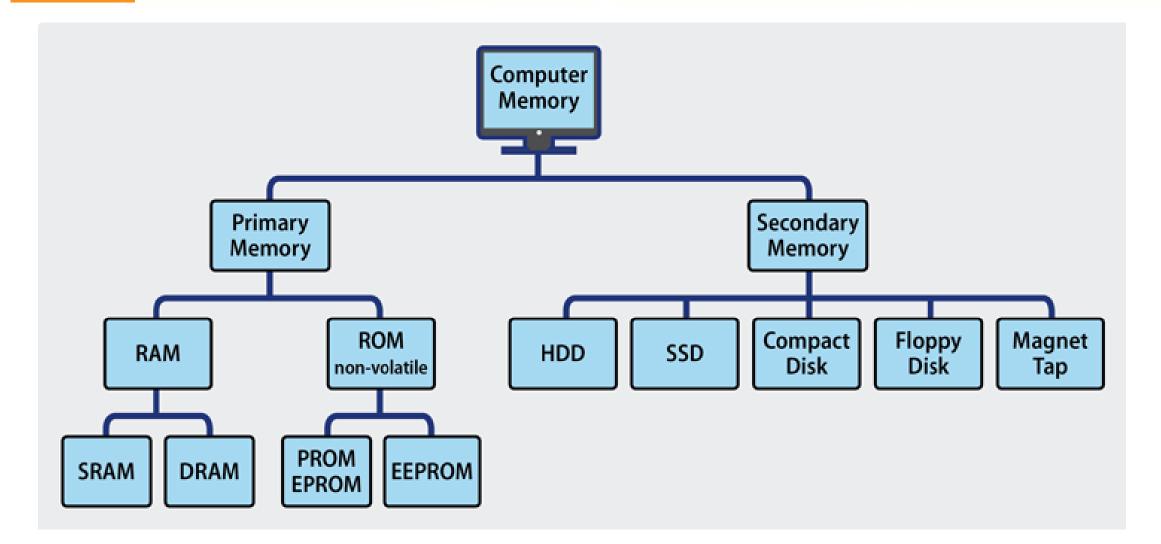

### **Memory Classification**

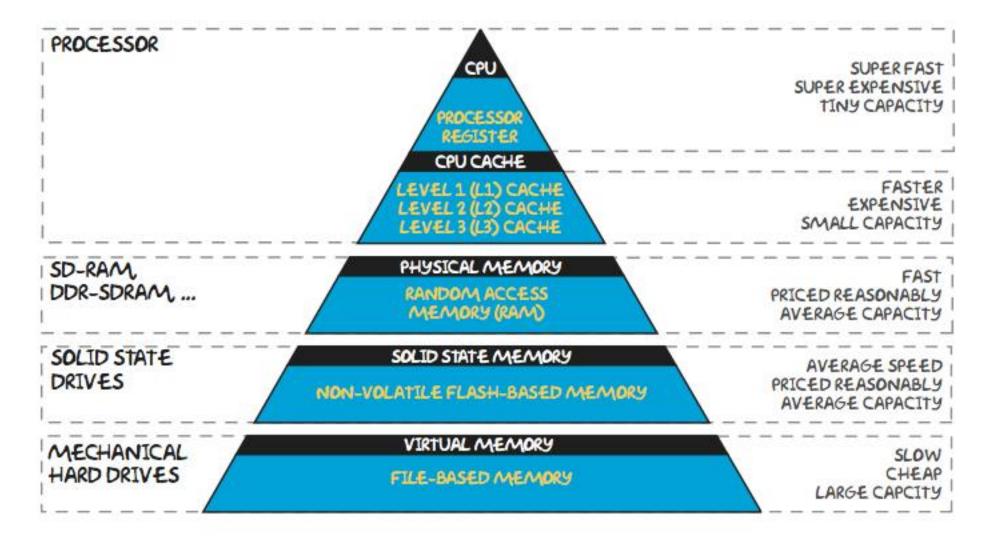

#### **Memory Hierarchy**

# Question

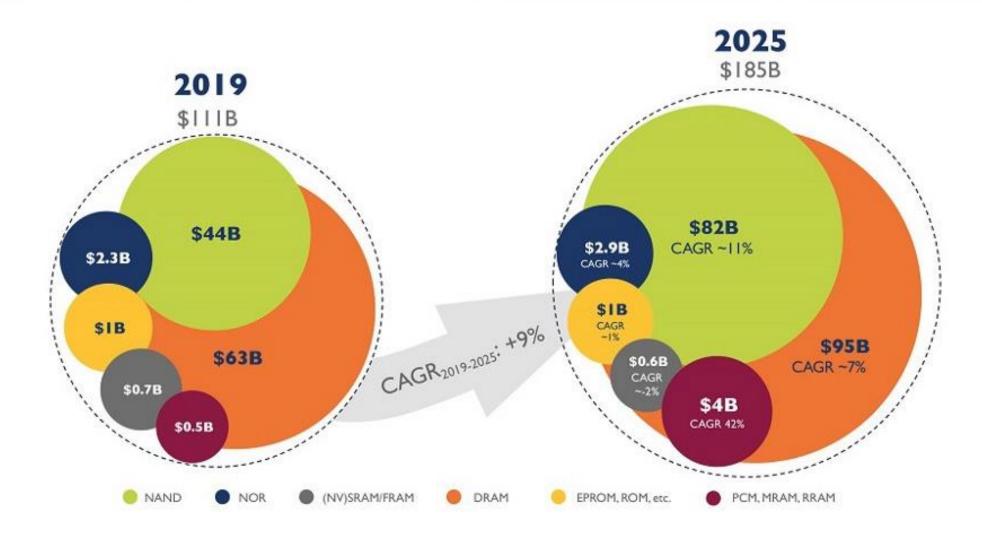

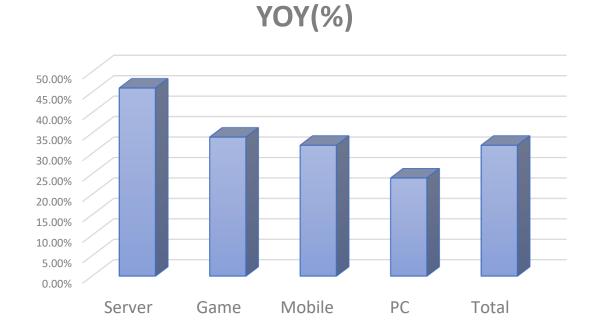

Which type of memory has the highest market cap growth in 5 years time?

Which type of memory has the highest CAGR in 5 years time?

### **Market of Memory**

**PHISON**

### **NAND Flash Is Everywhere**

PC Computer

Smartphone

Smart Speaker

Smart Robots

Google Glass

Drones

**PHISON**

Smart Treadmills

Smart Projectors

**Electric Cars**

**PHISON**

# Question

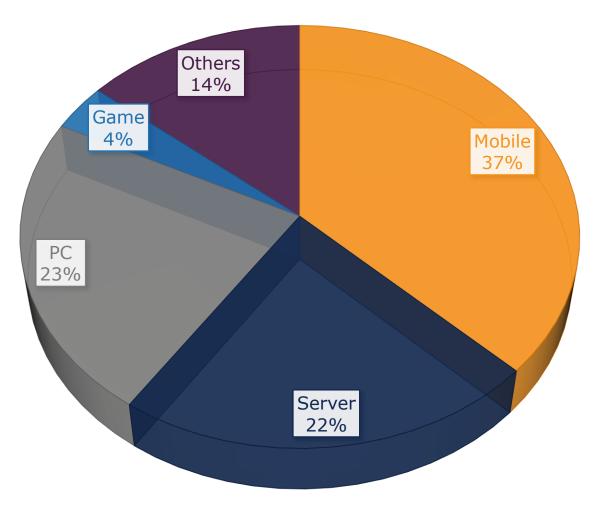

Which type of application used the most of NAND Flash?

Which type of application that uses NAND Flash has the highest growth?

# **Distribution and Trend by Applications**

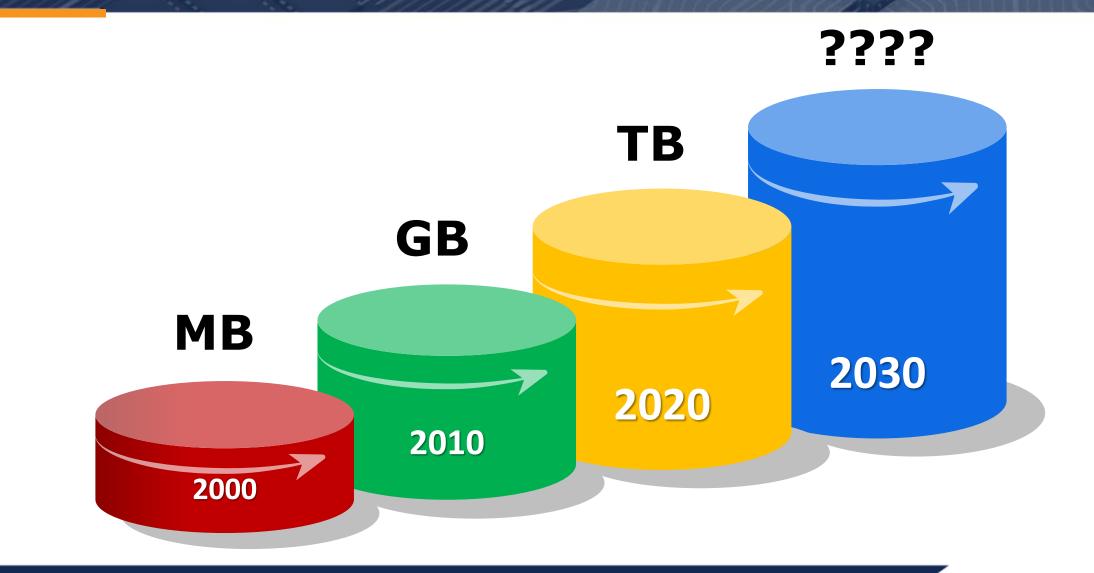

#### **Data Storage**

Floppy Disk

1.44MB

# **Optical Disc**

CD: 700MB DVD: 4.7GB Blu-ray Disc: 25GB~128GB HDD

36GB~1TB~Beyond

# **NAND Storage**

$1GB \sim 1TB \sim 8TB \sim Beyond$

# **Demand Never Stop**

# Question

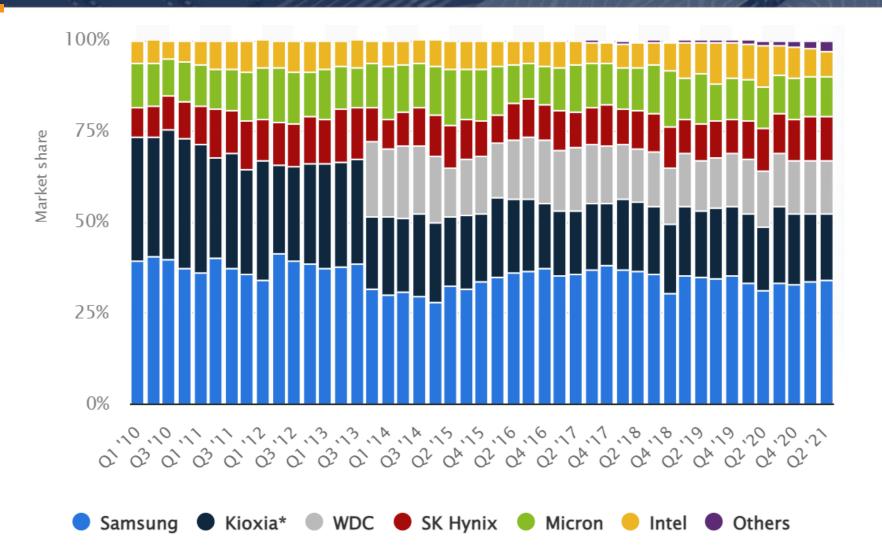

Which company invented NAND Flash?

A NAND Flash company founder used to be a farmer, guess what did he used to grow?

#### **NAND Flash Players**

**PHISON**

#### **NAND Flash Players**

**PHISON**

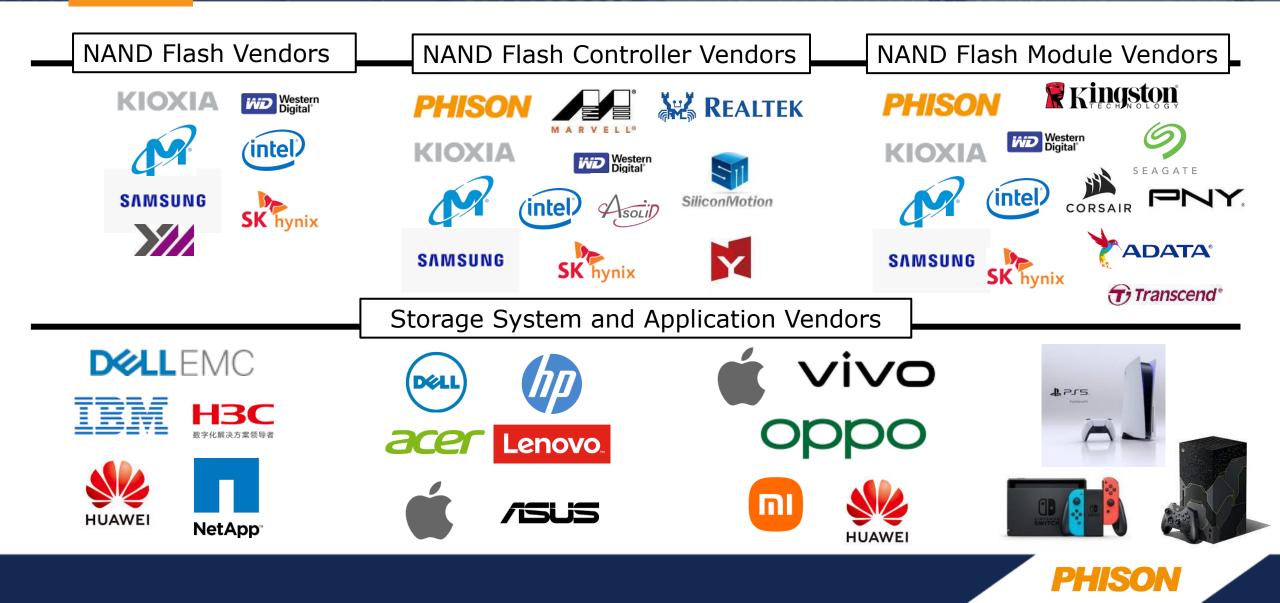

# ECO System of NAND Flash Storage System

#### **About Phison**

2000

2001

2002

2003

2004

2005

2006

2007

2008

2009

2010

2011

2012

2013

2014

2015

2016

2017

2018

2019

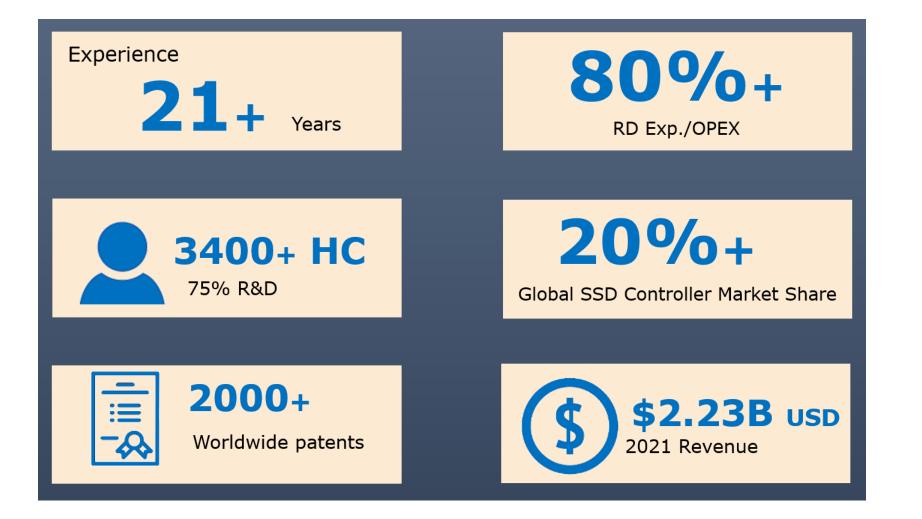

#### World No.1 20%+ Worldwide **Taiwan Top 4 IC Design House NAND Flash Controller SSD** Controller **Solution Market Share** Gaming Enterprise Automotive Industrial Embedded ODM **Technology-Leadership Application-Driven Consumer-Driven** 2,236 1800 **SSD** 1,600 .⊆ 1,400 Millions 1,200 USD 1,000 800 600 400 200 0

#### **PHISON**

2020

2021

#### **Key Facts**

#### Overview

CONFIDENTIAL

PHISON

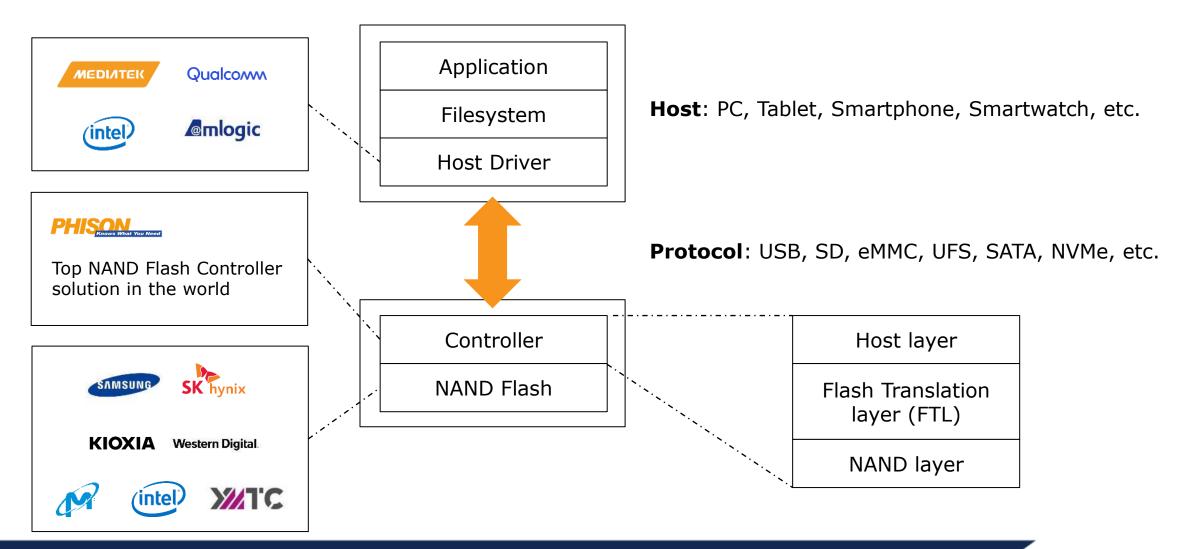

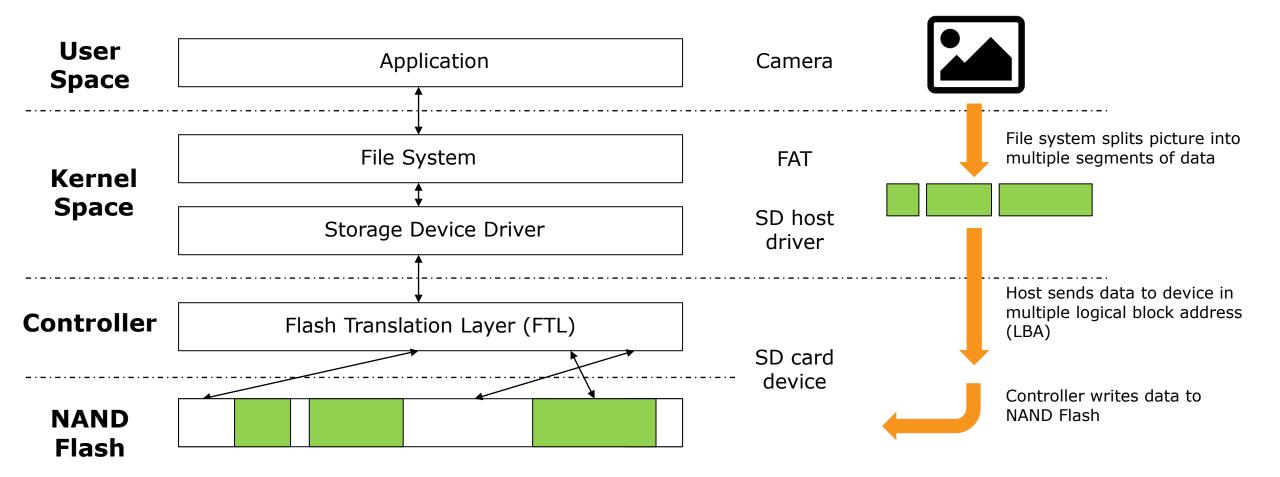

# **Application & Flash Storage Device**

CONFIDENTIAL

# **NAND Flash Device**

I II

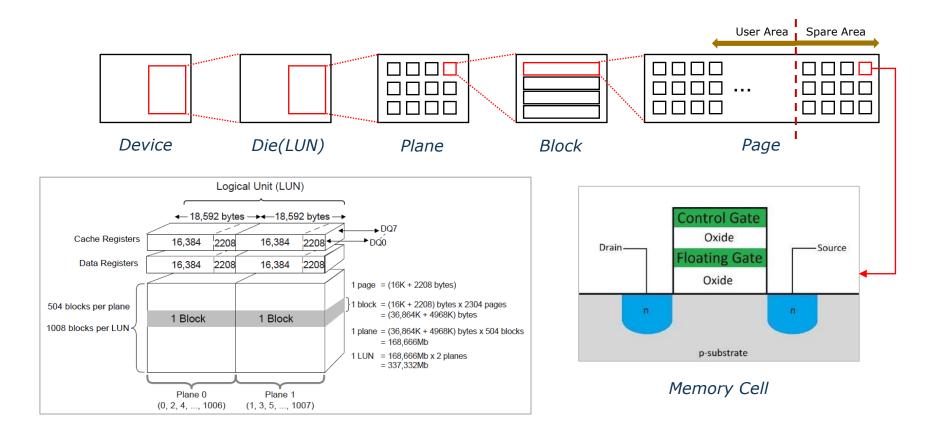

### **NAND Flash Structure**

CONFIDENTIAL

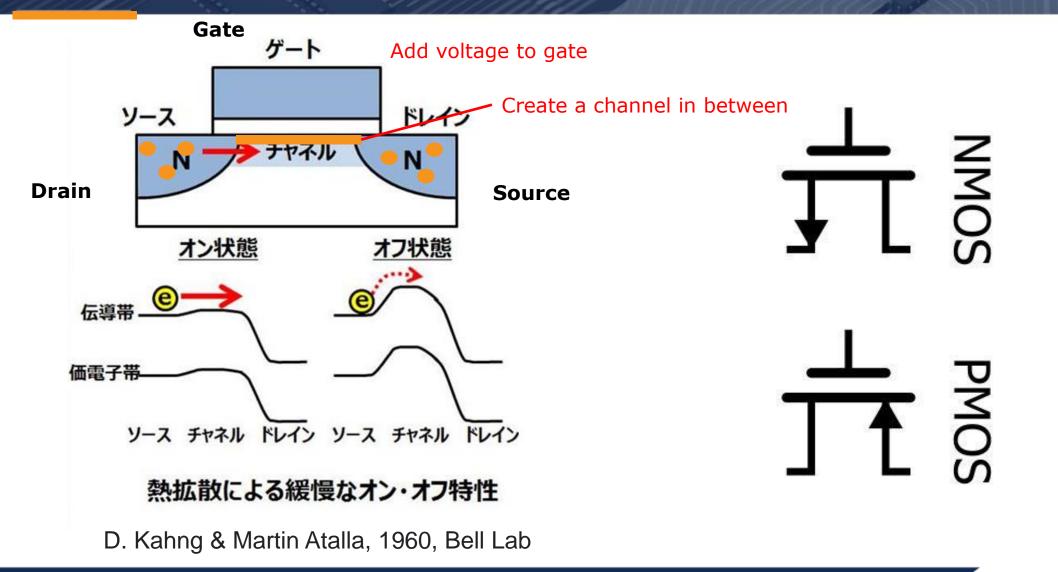

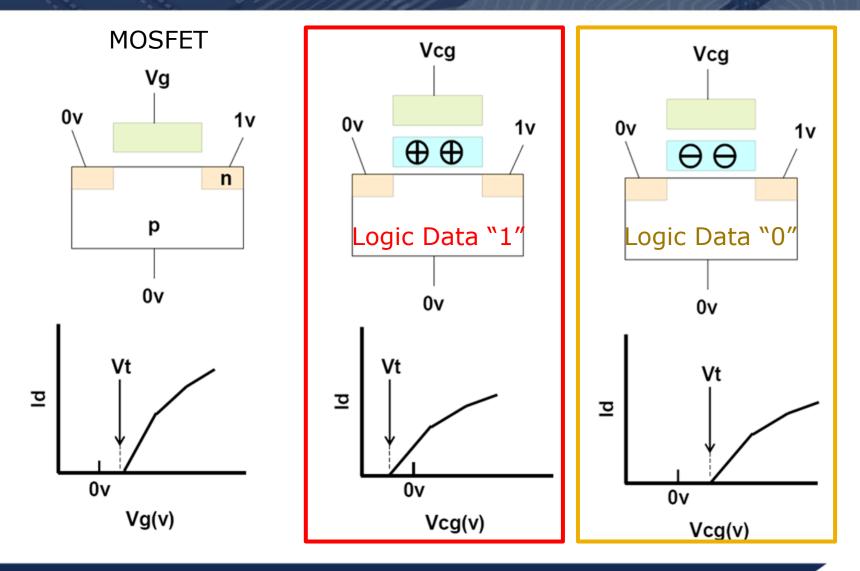

### What's MOSFET

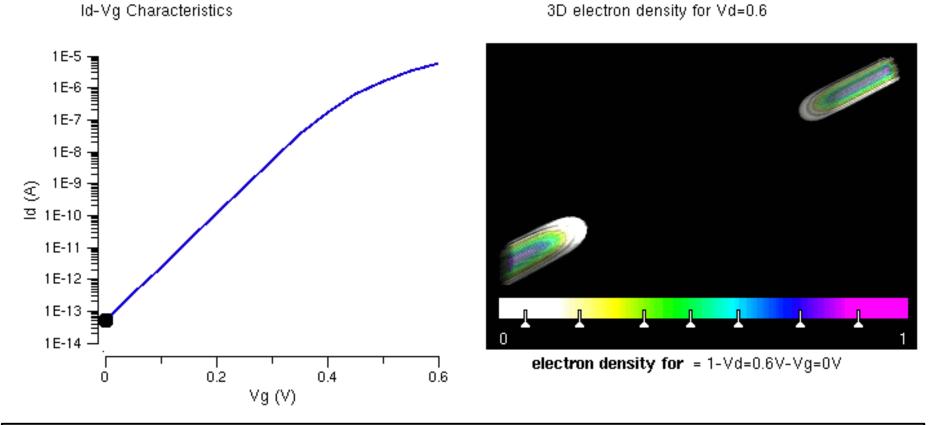

### What's Threshold Voltage?

As known as V<sub>th</sub>, V<sub>t</sub> :a gate voltage which can "turn on" the channel of a transistor.

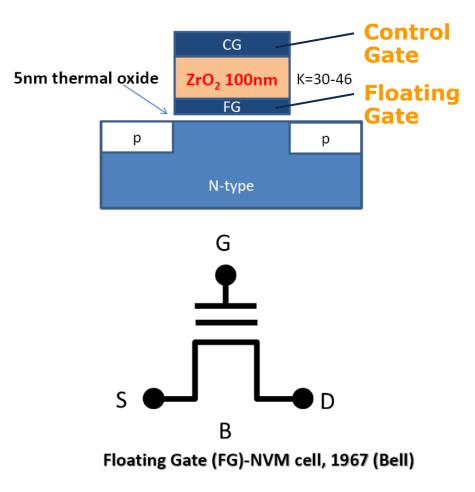

### What's Floating Gate MOSFET

✓ Electrically isolated

Charge contained in it remains unchanged for long periods of time

半導體之父施敏教授研發的「浮閘記憶體」

#### **Threshold Voltage of Memory Cell**

**PHISON**

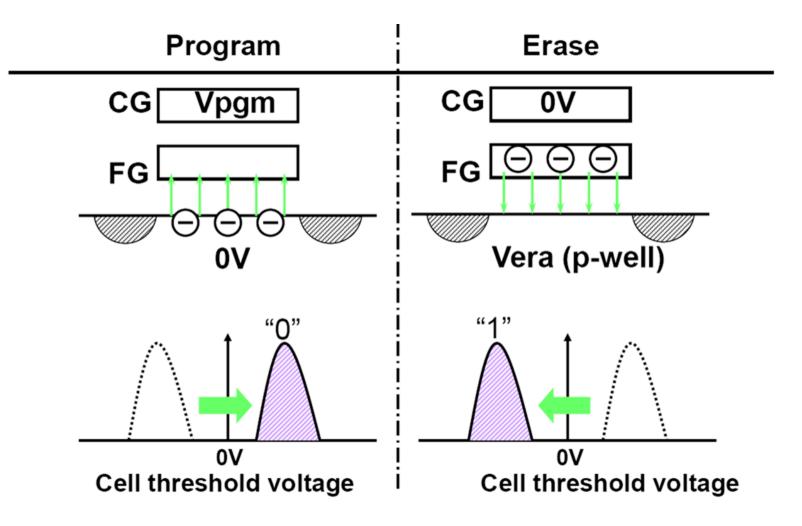

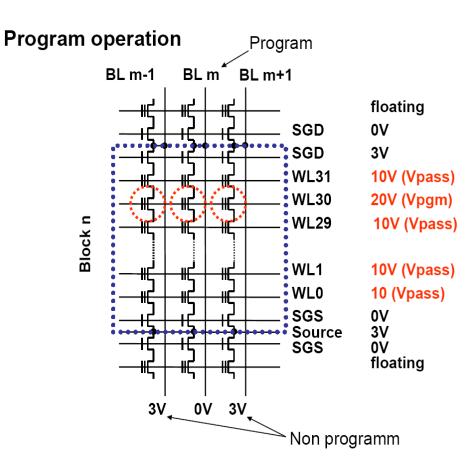

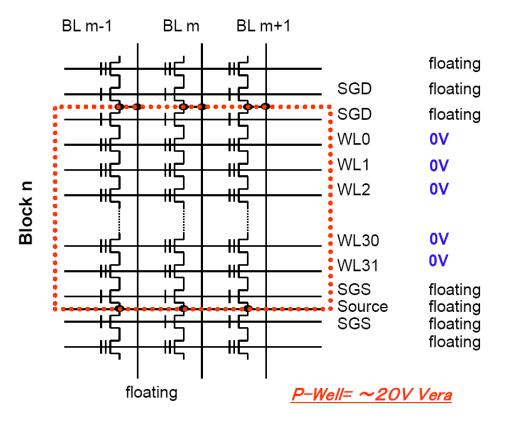

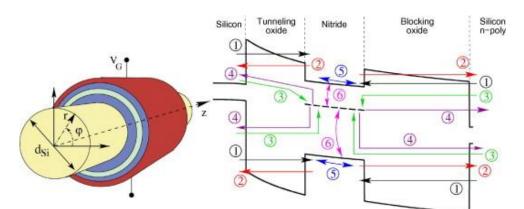

#### **Principle of NAND Memory Programming and Erasing**

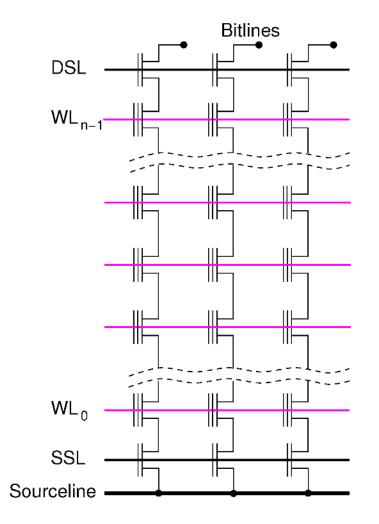

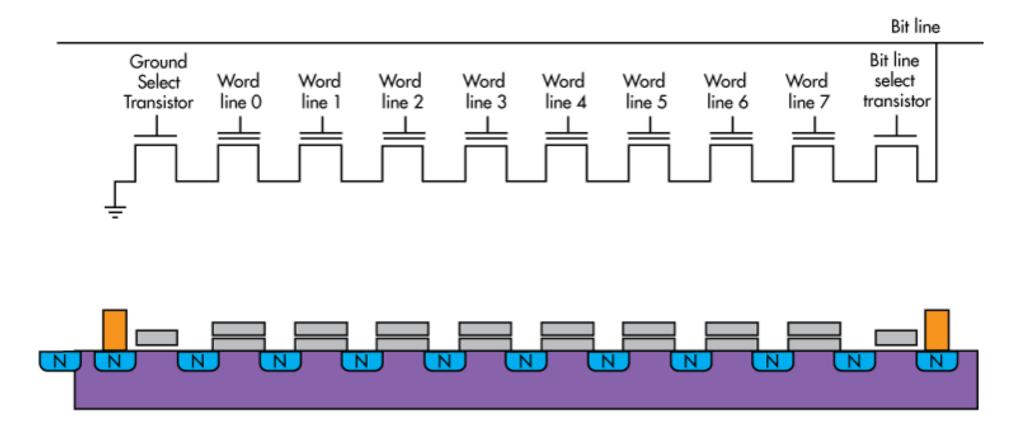

# NAND Flash Array

C)

**PHISON**

### **Basic Operation of NAND Flash- P/E**

#### Erase operation (Block erasing)

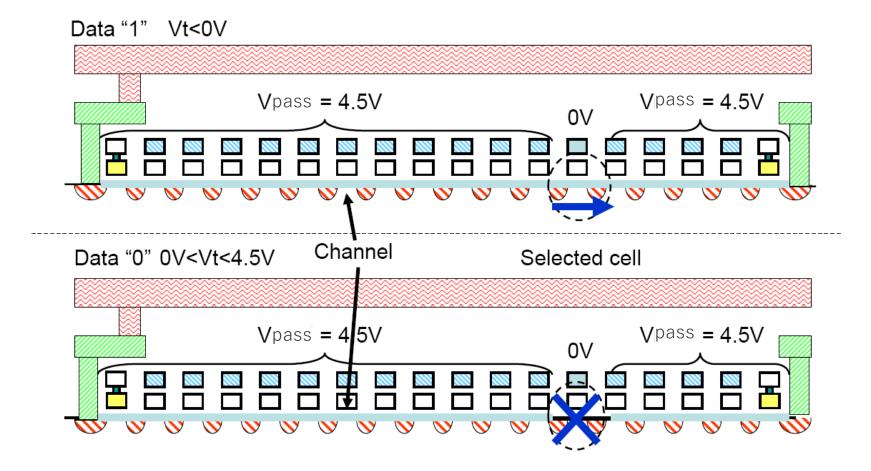

# **Basic Operation of NAND Flash- Read**

#### **Read Operation**

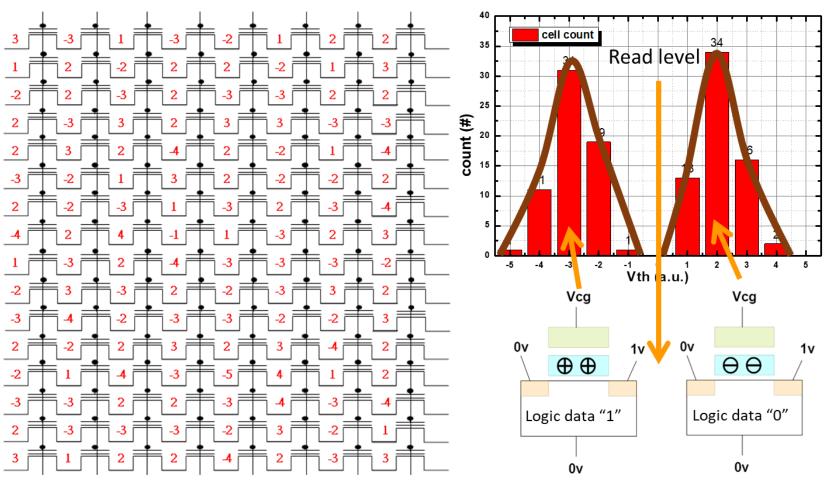

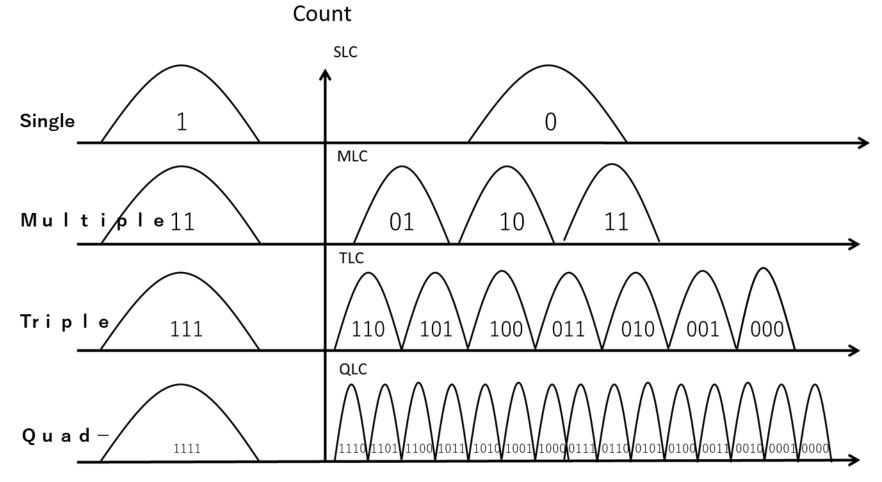

# **Threshold Voltage Distribution**

V<sub>th</sub> of a 128 bit NAND Array:

$V_{th}$  distribution of the array:

# **XLC** Application

Threshold voltage

# Question

# Why do we need XLC?

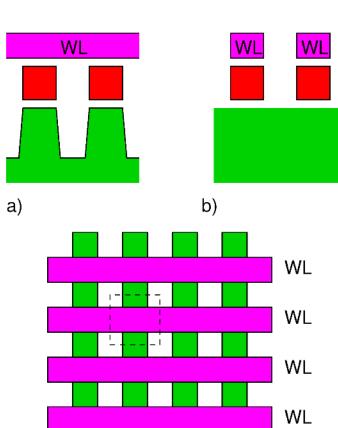

# 2D (Planar) NAND Flash

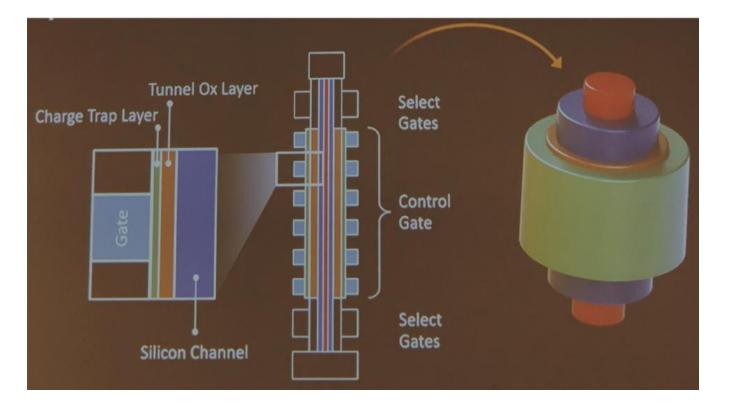

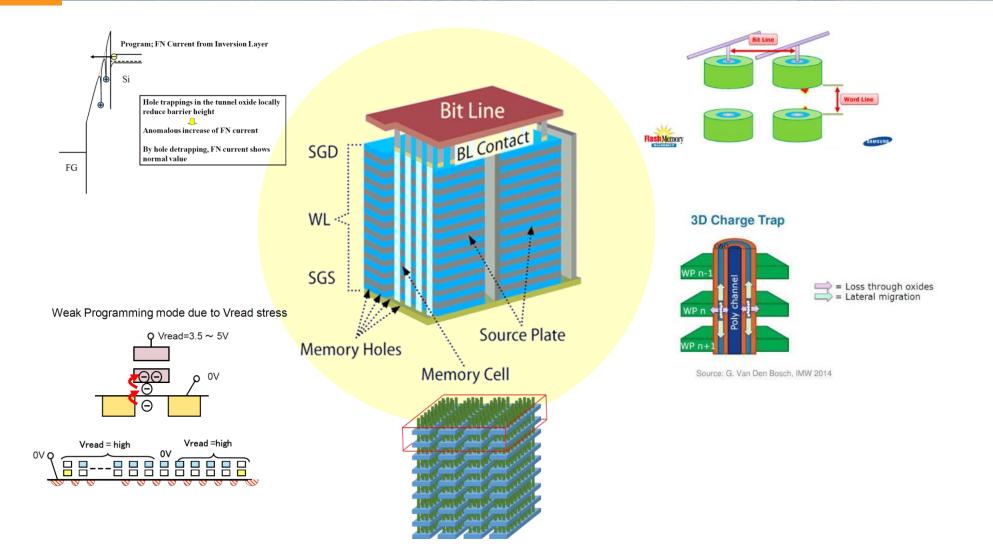

# **3D NAND Flash**

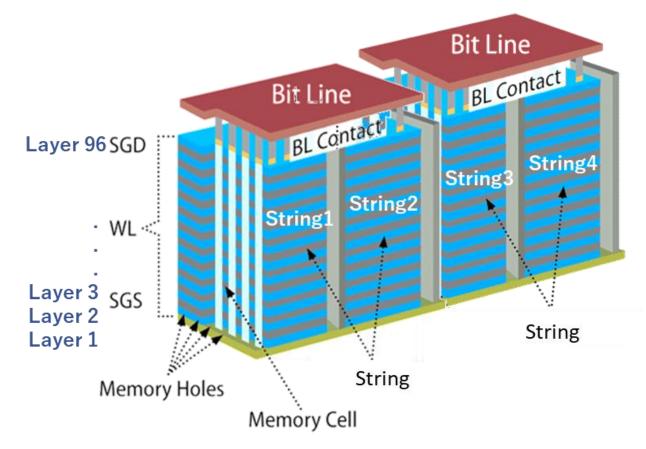

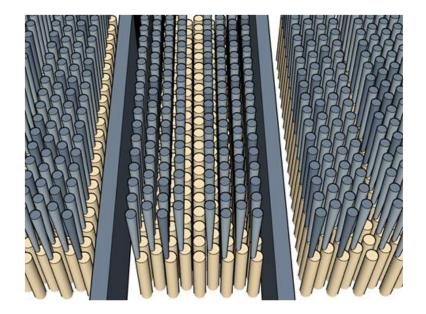

## **3D NAND Array**

#### 3D NAND Architecture

Page Size = 16K Byte (16\*1024\*8) 1 WL = 4 strings = 4 Pages 1Block = 4 \* 96 WLs = 384 Pages (SLC)

## Xtacking

## **Reliability Issues of NAND Flash**

## Question

Why do we need NAND Flash Controller?

What does NAND Flash Controller need to do?

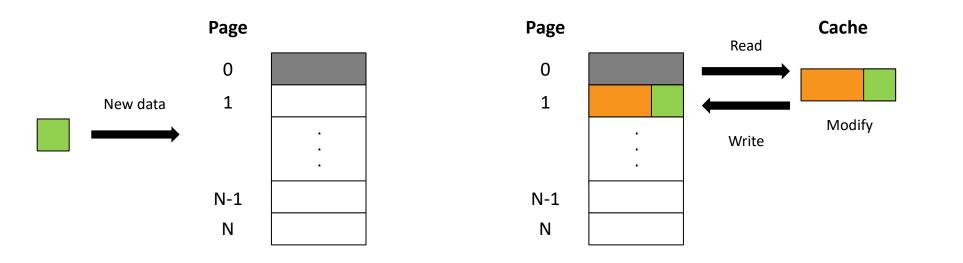

- Page is the smallest unit for read and program

- Block is the smallest unit for erase

- Must erase before program (cannot overwrite)

## Mapping Table & Garbage Collection

• Each read/program/erase operation has busy time to complete I/O scheduling

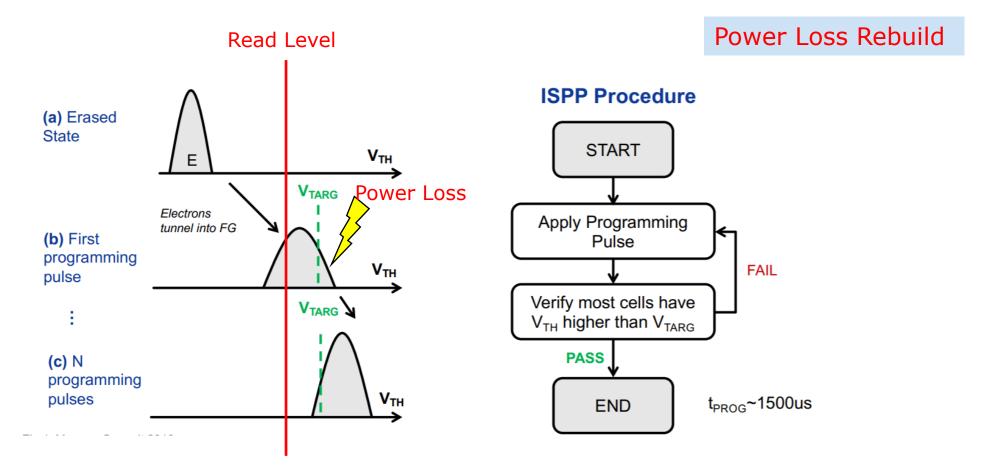

• What if sudden power loss happens before VT reaches programmed state?

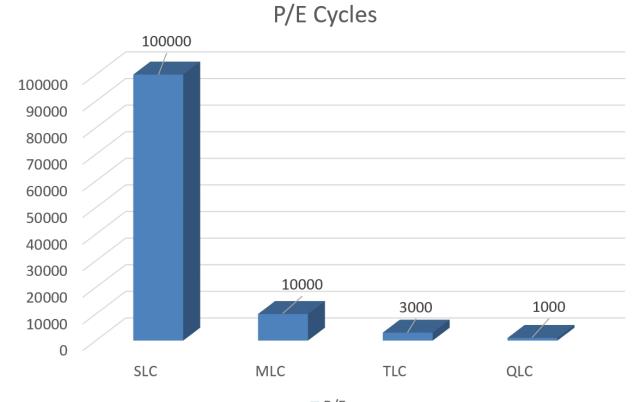

- Program/Erase (PE) Cycle: SLC = 100k, MLC = 10k, TLC = 3k Wear Leveling

- Initial and runtime bad blocks Bad Block Management

P/E

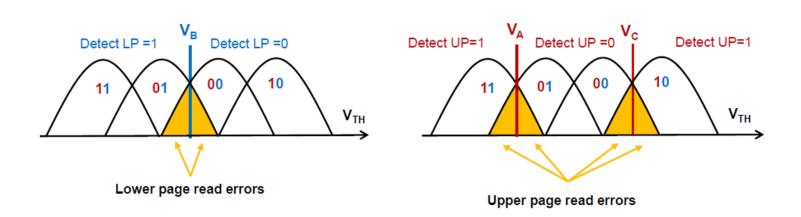

- Main sources of noise that would cause abnormal Vth distribution and read errors:

- Program/Erase cycling stress: Program/erase pulses lead to degraded reliability of the underlying NAND flash cells.

- **Cell-to-cell interference**: Threshold voltage of 'victim' cell is strongly affected by programming of neighboring 'aggressor' cells.

- **Data retention**: Over time, electrons can escape from the programmed flash cells, causing a loss of threshold voltage.

- **Read disturbance**: When reading a particular page in a block of NAND flash, a voltage is applied to all other WL in order to 'deselect' them. This applied voltage can affect the Vth distribution of the unselected WLs.

Error correction code & Read disturb management

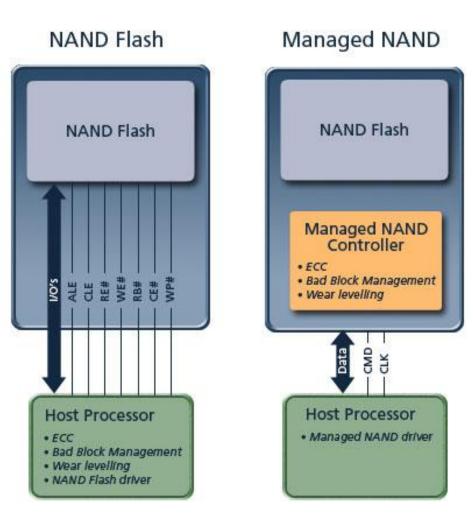

## **NAND Flash Controller**

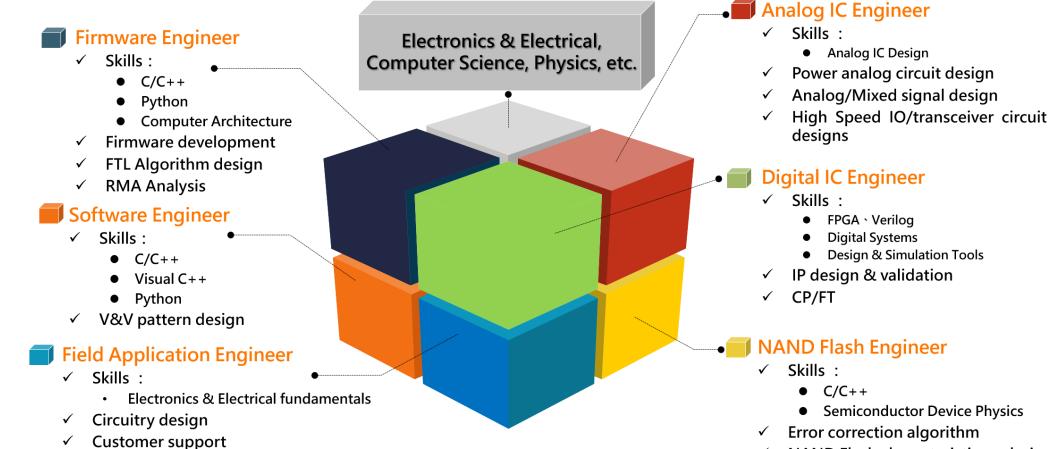

## **Key Departments in Controller House**

✓ NAND Flash characteristic analysis

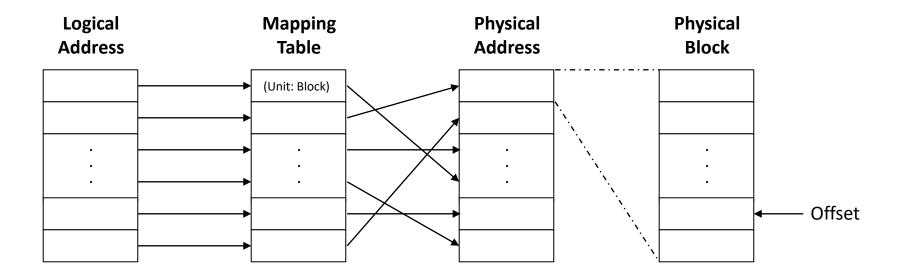

# **Block Base Mapping**

TIL

#### **Definitions & Rules**

- 8GB NAND Flash

- 1 die = 2048 blocks

- 1 block = 256 pages

- 1 page = 16KB = 32 sectors

- 1 LBA/sector = 512B

- Limitation

- **Page** is the smallest unit for read and program

- **Block** is the smallest unit for erase

- Must erase before program (cannot overwrite)

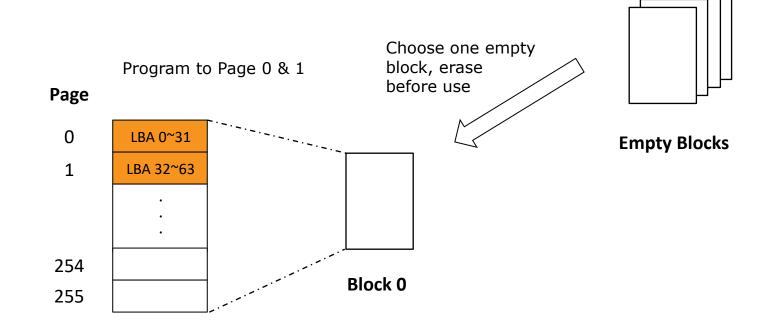

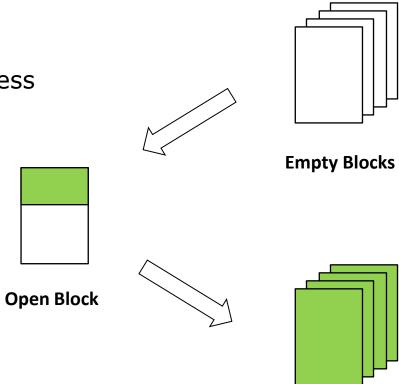

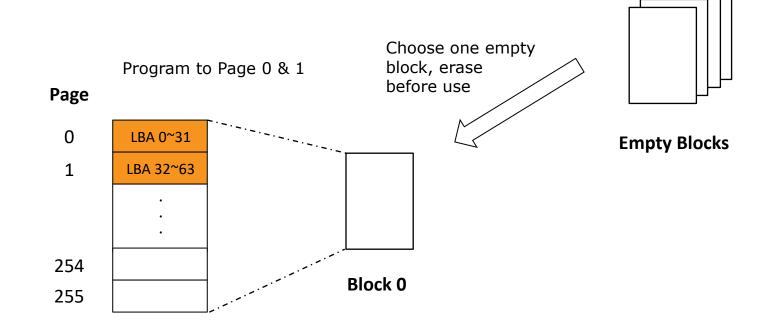

## Write

- Host writes 2 chunk of data (16KB each)

- LBA 0~31

- LBA 32~63

#### Write

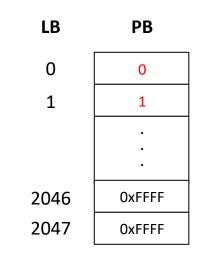

#### Q: How do we build mapping table?

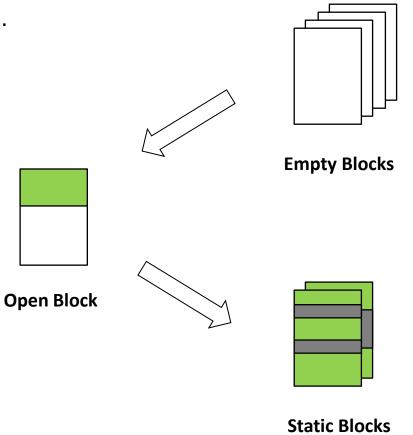

- Host continues to write large chunk size data...

- Open block becomes static when full

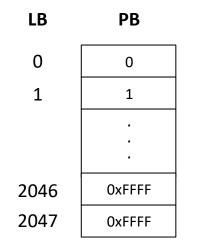

- We record logical to physical block mapping

- Each Logical Block (LB) index maps to Block (PB) address

- Address = (PB)

- Might need 2B to store address

**Static Blocks**

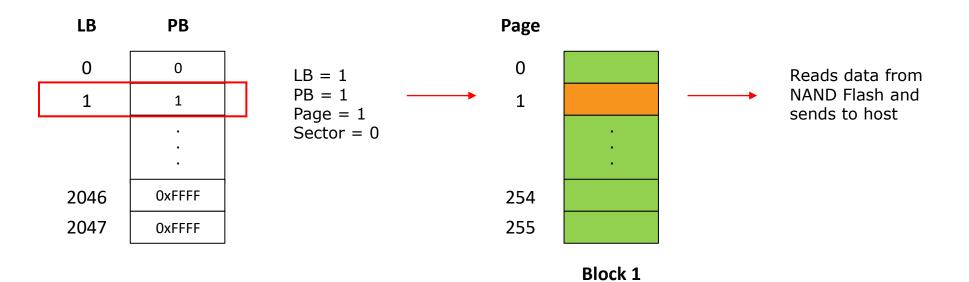

- Host wants to read LBA 32~63

- How do we know where is the data located in NAND Flash?

Logical to Physical (L2P) translation

```

Step 1: Calculate Logical Block (LB) Index

```

LBA

LB =

Total Physical Sector Number (in block)

Step 2: Get Physical Block (PB) address from mapping table

Step 3: Calculate Offset

Page

LBA % Total Physical Sector Number (in block)

= Total Physical Sector Number (in page)

Sector = LBA % Total Physical Sector Number (in block) % Total Physical Sector Number (in page)

#### Read

• Host wants to read LBA 8224~8255

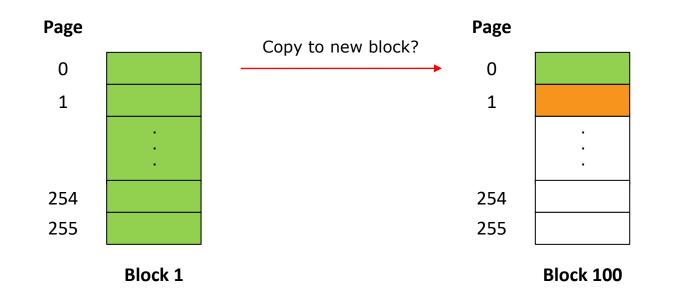

#### Overwrite

#### Q: How do we handle overwrite page?

- What if host overwrites same address LBA 8224~8255?

- Remember, we cannot overwrite a page that has been programmed

• Not so efficient

## Table Size (for Block Mapping)

- For 8GB NAND Flash, total table size required is 4KB

- Table Size = 2048 blocks × 2B = 4KB

- Table Entries = 2048

#### **Block Base Mapping Table**

In a block level address mapping, a logical page address is made up of both a logical block number and an offset

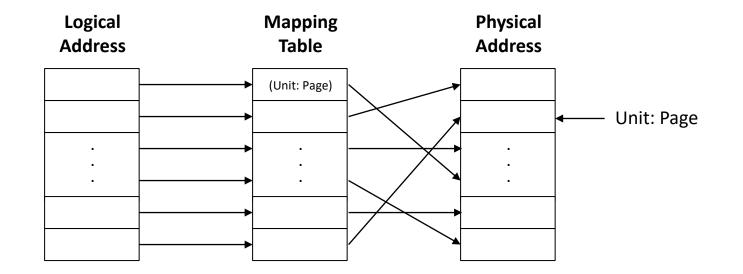

# Page Base Mapping

$( \square$

CONFIDENTIAL

LU

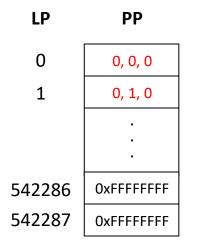

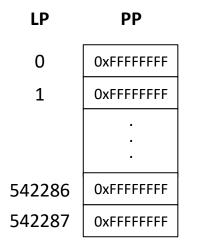

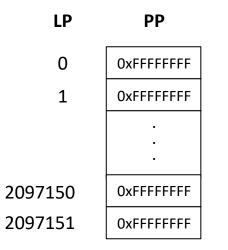

## Page Base Mapping Table

In a page level address mapping, a logical page can be mapped into any physical page in flash memory

#### Page Base Mapping Table

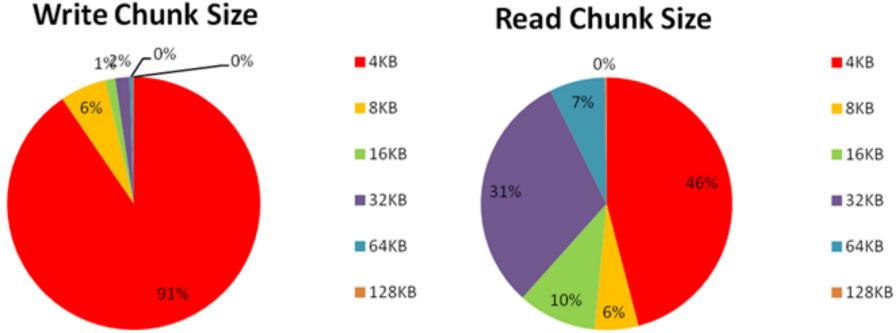

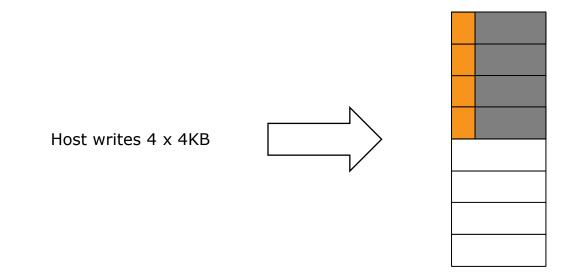

- Data structure of host (eMMC) operations on WHCK performance test

- 4KB chunk size has higher percentage than other chunk size

**Read Chunk Size**

## Write

- Host writes 2 chunk of data (16KB each)

- LBA 0~31

- LBA 32~63

- Instead of block mapping, we now record logical to physical page mapping

- Each Logical Page (LP) index maps to Physical Page (PP) address

- Address = (Block, Page, Sector)

- Might need 4B (instead of 2B) to store address

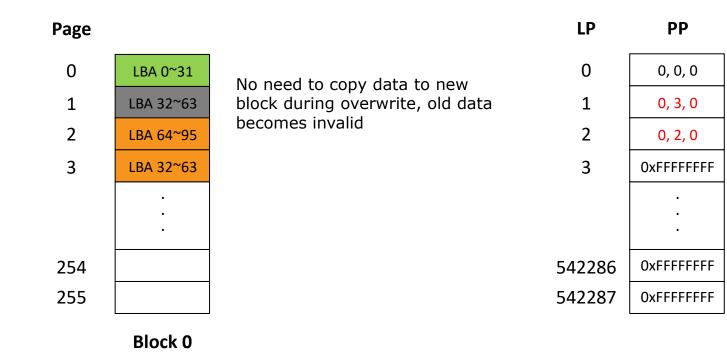

## Write

- Host writes additional 2 chunk of data (16KB each)

- LBA 64~95

- LBA 32~63 (overwrite)

**PHISON**

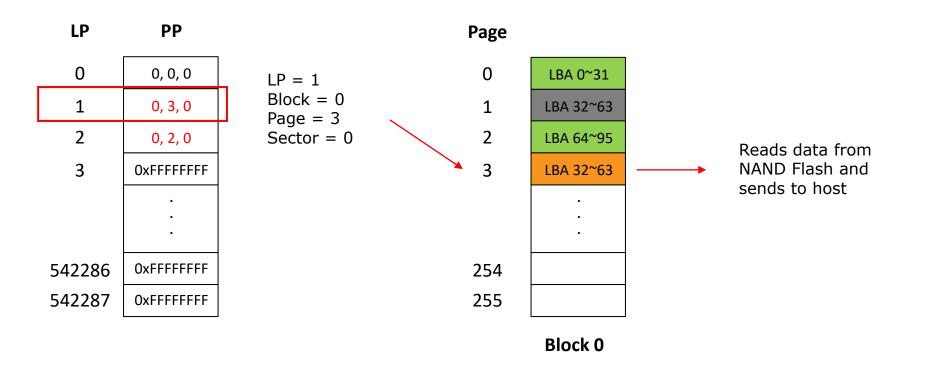

- Host wants to read LBA 32~63

- How do we know where is the data located in NAND Flash?

Logical to Physical (L2P) translation

```

Step 1: Calculate Logical Page (LP) Index

```

LBA

LP =

Total Physical Sector Number (in page)

Step 2: Get Physical Page (PP) address from mapping table

#### Read

Host wants to read LBA 32~63

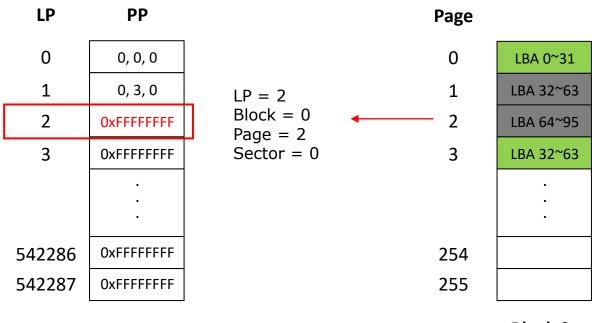

#### Erase

#### Q: How do we erase LBA?

Host wants to erase LBA 64~95

Block 0

• Mark corresponding LP as invalid

## Table Size (for 16KB Page Mapping)

- For 8GB NAND Flash, total table size required is 2MB

- Table Size = 2048 blocks × 256 pages × 4B = 2MB

- Table Entries = 2048 blocks × 256 pages = 524288

## Table Size (for 4KB Page Mapping)

- For 8GB NAND Flash, total table size required is 8MB

- Table Size = 2048 blocks × 256 pages × 4 nodes × 4B = 8MB

- Table Entries = 2048 blocks × 256 pages × 4 nodes= 2097152

# Garbage Collection (GC)

CONFIDENTIAL

LU

## **Garbage Collection**

- What is GC and why do we need to do GC?

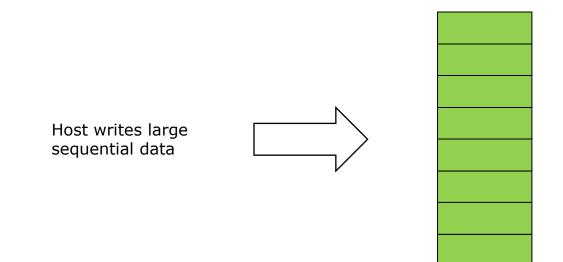

- Host continues to write large chunk size data...

- Open block becomes static when full

- Some physical page become invalid

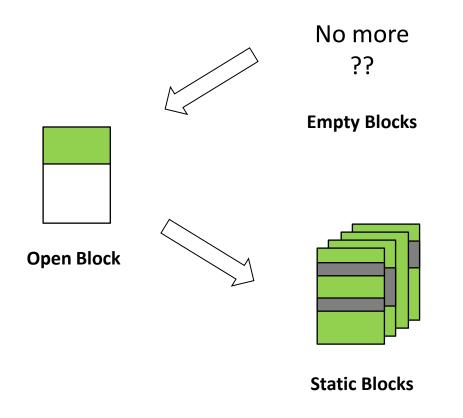

## **Garbage Collection**

- What if host keeps writing until empty block runs out?

- Before empty block runs out, we should do Garbage Collection (GC)

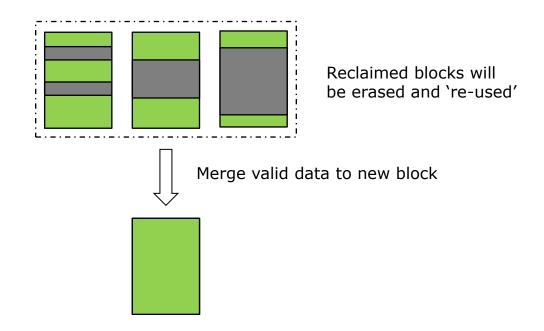

## **Garbage Collection**

- · We collect valid data to new block and reclaim blocks filled with invalid data

- So that we can erase the reclaimed blocks and use them for new data

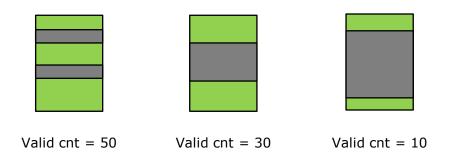

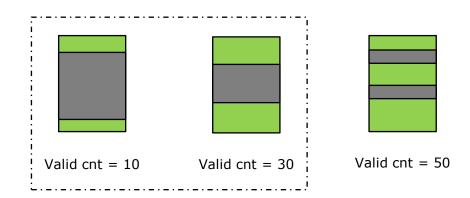

## **Garbage Collection**

• How do we pick static blocks as source of GC?

Pick the block(s) with least valid count

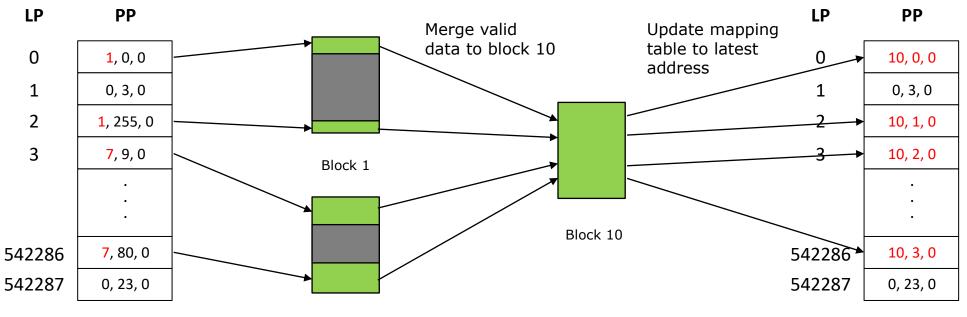

### **Garbage Collection**

### Q: What should we update to complete GC?

- How do we know which data is valid or invalid in the source blocks?

- Check the mapping table, look for the entries that point to these source blocks

Block 7

# Write Amplification Factor (WAF)

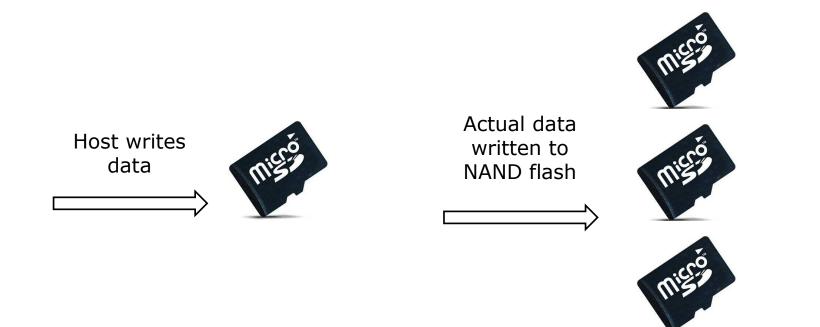

## Definition

*Write Amplification Factor* (WAF) =

Data written to NAND Flash

Data written by host

## Example

• WAF = 1

### Example

• WAF = 4

Still remember what happens when host overwrites data of same LBA using block level mapping?

## Summary

- Disadvantages of high WAF

- Low performance

- High erase count

### **Terabytes Written (TBW)**

• Total amount of data that can be written to a storage device until it reaches its lifetime

User Capacity (GB)  $\times$  NAND P/E Cycles

*Terabytes Written (TBW)* =

$W\!AF \times 1024$

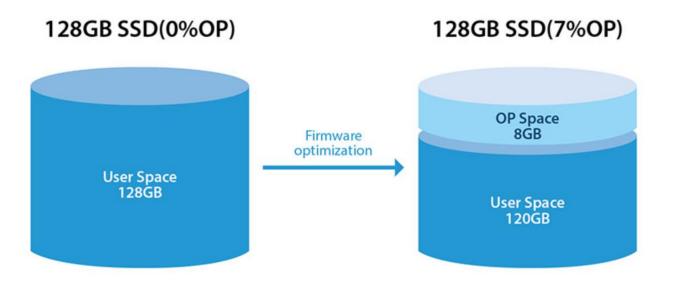

# **Over Provision (OP)**

### Definition

Over-Provision = Physical capacity – User capacity User capacity

### Example

The larger the size of the spare area, the higher the operating efficiency, and the better the performance become

The Sliding Puzzle

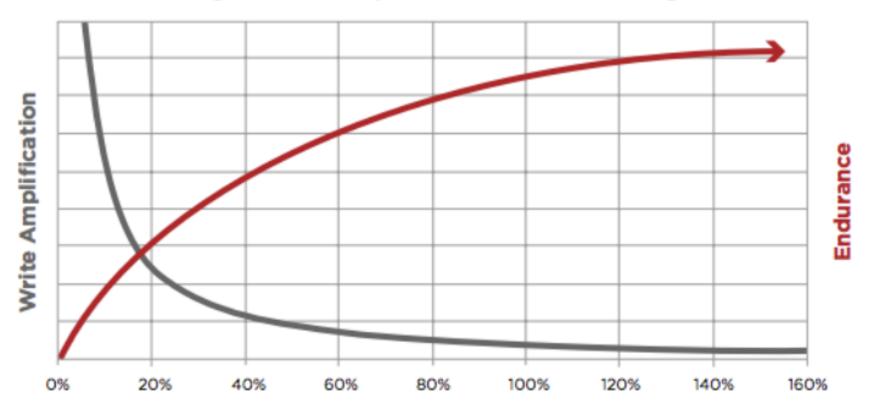

**OP vs WAF**

Figure 2: Write Amplification vs. Over Provisioning

Overprovisioning (%)

### Summary

- Advantage(s) of higher OP due to less background data movement required

- Higher performance

- Better endurance (lower WAF)

- Disadvantage(s) of higher OP due to more reserved spare blocks

- Less usable storage space

## **NAND Flash Limitation**

- **Page** is the smallest unit for read and program

- **Block** is the smallest unit for erase

- Must erase before program (cannot overwrite)

### Q: Page vs Block Base, which is better?

|                        | Page Base                                                    | Block Base                                                           |

|------------------------|--------------------------------------------------------------|----------------------------------------------------------------------|

| Mapping Unit           | Page (or 4KB)                                                | Block                                                                |

| Table Size             | Large (store in NAND Flash)                                  | Small (store in SRAM)                                                |

| <b>R/W Performance</b> | Excellent random write<br>performance                        | Slow random write performance,<br>but impressive read<br>performance |

| Garbage Collection     | Collect valid nodes when empty<br>block becomes insufficient | Collect valid nodes when<br>overwrite previous data or erase<br>data |

| WAF                    | Low (efficient block utilization)                            | High (expensive merge operation)                                     |

## **Cold Facts**

- Do you know that your storage device with higher OP (less user space) has better performance and lifetime?

- Do you know that when you keep your storage usage full, the performance and lifetime become worst (due to frequent GC operation)?

- When purchasing storage device, consider performance vs lifetime (such as WAF or TBW)

## **Advanced Questions**

- What if power cycle occurs when we program NAND Flash?

- What if bad block occurs when we program NAND Flash?

- What if read error occurs when we read NAND Flash?

- What if certain blocks wear out quickly than other blocks?

| Table Management   |                         |  |

|--------------------|-------------------------|--|

| Garbage Collection | Read Disturb Management |  |

| Wear Leveling      | Bad Block Management    |  |

| Power-up Rebuild   |                         |  |

## **THANK YOU!**